# TECHNICAL MANUAL FOR

# AM-100

2-BOARD 16-BIT CPU

DWM-00100-00

# 2-BOARD 16-BIT CPU

Manufactured By

ALPHA MICROSYSTEMS 17881 SKY PARK NORTH IRVINE, CALIFORNIA 92714

#### PROPRIETARY NOTICE

17 mar

This document and the information herein disclosed is the proprietary property of ALPHA MICRO, 17881 Sky Park North, Irvine, California 92714. Any person or entity to whom this document is furnished or having possession thereof, by acceptance, assumes custody thereof and agrees that the document is given in confidence and will not be copied or reproduced in whole or in part, nor used or revealed to any person in any manner except to meet the purposes for which it was delivered. Additional rights and obligations regarding this document and its contents may be defined by a separate written agreement with ALPHA MICRO-SYSTEMS, and if so, such separate written agreement shall be controlling.

"AMOS," "Alpha BASIC," and "AM-100" are trademarks of products and software of ALPHA MICROSYSTEMS, Irvine, California -92714 © 1978, 1979, ALPHA MICROSYSTEMS.

|   |       | USER COMMENTS | TECHNICAL PUBLICATIONS FILE REFERENCE                                                                            |

|---|-------|---------------|------------------------------------------------------------------------------------------------------------------|

| - | FROM: | NAME          |                                                                                                                  |

| Ĭ |       | ADDRESS       | NOTE: Use this form to communicate any errors,<br>suggested changes, or general comments<br>about this document. |

|   |       | CITY          | If necessary, call us at:<br>(714) 957-6076                                                                      |

|   |       | STATE ZIP     |                                                                                                                  |

DOCUMENT: TITLE/NUMBER/REVISION\_\_\_\_\_

## COMMENTS:

÷ .

-----

して 古い いい

# TABLE OF CONTENTS

.

# Paragraph

٠

# Page.

-

|                                                                           | SECTION 1 GENERAL DESCRIPTION                                                                                                                                                  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                                                                       | Introduction                                                                                                                                                                   |

| 1.1                                                                       | Circuit Board Description 1-1                                                                                                                                                  |

| 1.2                                                                       | Application 1-2                                                                                                                                                                |

|                                                                           |                                                                                                                                                                                |

|                                                                           | SECTION 2 OPERATING DATA                                                                                                                                                       |

| 2.0                                                                       | Introduction                                                                                                                                                                   |

| 2.1                                                                       | Capabilities and Specifications 2-1                                                                                                                                            |

| 2.2                                                                       | Interface Description and Wiring 2-2                                                                                                                                           |

| 2.3                                                                       | User Options                                                                                                                                                                   |

| 2.4                                                                       | Interrupt and DMA Options 2-8                                                                                                                                                  |

| 2.5                                                                       | System Connections                                                                                                                                                             |

|                                                                           |                                                                                                                                                                                |

|                                                                           | SECTION 3 PROGRAMMING                                                                                                                                                          |

| 3.0                                                                       |                                                                                                                                                                                |

| 5.0                                                                       | Introduction                                                                                                                                                                   |

| 3.1                                                                       | Introduction3-1System Configuration3-1                                                                                                                                         |

|                                                                           |                                                                                                                                                                                |

| 3.1                                                                       | System Configuration                                                                                                                                                           |

| 3.1<br>3.2                                                                | System Configuration3-1Software Overview3-5Operating System3-5                                                                                                                 |

| 3.1<br>3.2<br>3.2.1                                                       | System Configuration3-1Software Overview3-5Operating System3-5                                                                                                                 |

| 3.1<br>3.2<br>3.2.1<br>3.2.2                                              | System Configuration3-1Software Overview3-5Operating System3-5Assembly Language Program3-5                                                                                     |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3                                     | System Configuration3-1Software Overview3-5Operating System3-5Assembly Language Program3-5Text Editor3-6                                                                       |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3<br>3.2.4                   | System Configuration3-1Software Overview3-5Operating System3-5Assembly Language Program3-5Text Editor3-6Utility and Sort Programs3-6                                           |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3<br>3.2.4<br>3.2.5          | System Configuration3-1Software Overview3-5Operating System3-5Assembly Language Program3-5Text Editor3-6Utility and Sort Programs3-6Alphabasic Program3-6                      |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | System Configuration3-1Software Overview3-5Operating System3-5Assembly Language Program3-5Text Editor3-6Utility and Sort Programs3-6Alphabasic Program3-6Accounting Package3-7 |

÷.

Paragraph

|         | SECTION 4 FUNCTIONAL THEORY OF OPERATION |                |

|---------|------------------------------------------|----------------|

| 4.0     | Introduction                             | 4 - 1          |

| 4.1     | CPU Configuration                        | 4-1            |

| 4.1.1   | AM-100 Two-Board Set                     | 4-1            |

| 4.1.2   | S-100 Bus Operation                      | 4 - 2          |

| 4.1.3   | CPU Chip Set                             | 4-16           |

| 4.1.3.1 | Data Chip                                | 4 <b>-</b> 16  |

| 4.1.3.2 | Control Chip                             | 4-18           |

| 4.1.3.3 | Microm Chips                             | 4 <b>-</b> 18  |

| 4.1.3.4 | Microinstruction Bus                     | 4 - 18         |

| 4.2     | CPU Operations                           | 4-21           |

| 4.2.1   | Clock Generator                          | 4 <b>-</b> 34  |

| 4.2.2   | State Code Decoder Logic                 | 4-35           |

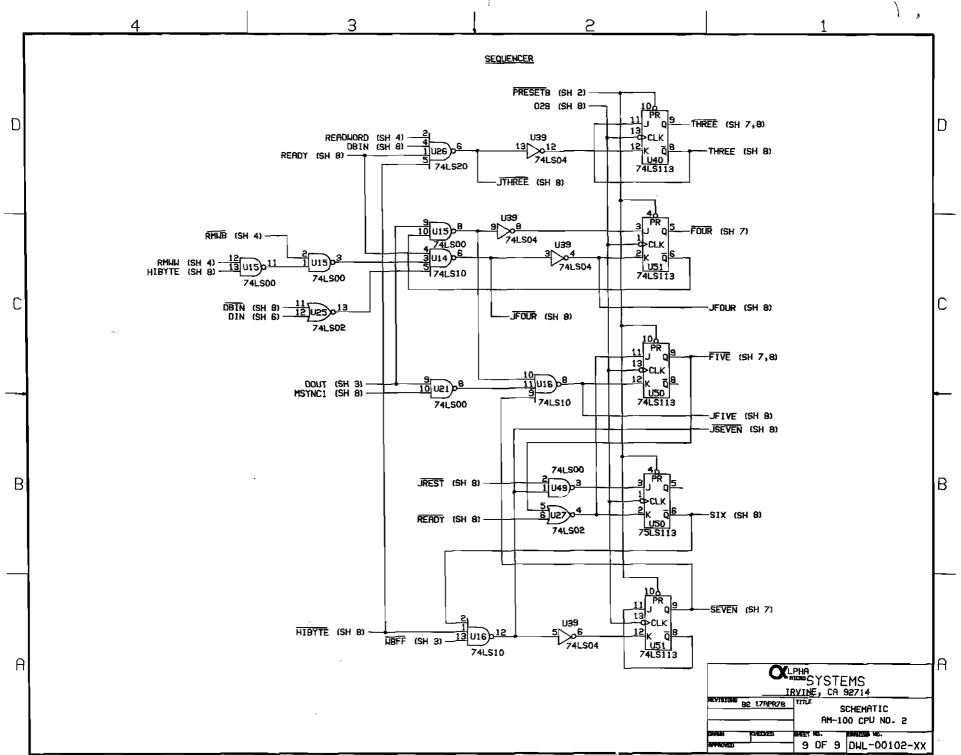

| 4.2.3   | Sequencer Operation                      | 4 - 35         |

| 4.2.4   | Initialization and Status                | 4 <b>-</b> 4 7 |

| 4.2.5   | Data Access                              | 4 <b>-</b> 4 8 |

| 4.2.5.1 | Addressing Operations                    | 4-50           |

| 4.2.5.2 | Write Operations                         | 4-50           |

| 4.2.5.3 | Read Operations                          | 4 <b>-</b> 51  |

| 4.2.6   | DMA and Interrupt Operations             | 4-51           |

| 4.2.6.1 | CPU Chip Set Interrupts                  | 4 <b>-</b> 5 2 |

| 4.2.6.2 | Vectored Interrupts                      | 4 <b>-</b> 5 3 |

| 4.2.6.3 | DMA Operations                           | 4 - 5 3        |

| 4.3     | CPU Microprocessor Chip Set Description  | 4 <b>-</b> 5 4 |

| 4.3.1   | System Components                        | 4 - 5 8        |

| 4.3.1.1 | Registers                                | 4 - 59         |

| 4.3.1.2 | Instruction Address Generation           | 4 - 64         |

| 4.3.1.3 | Microinstruction Bus                     | 4 - 6 5        |

| 4.3.1.4 | Data Access Bus                          | 4-66           |

| 4.3.1.5 | Microinstruction Storage                 | 4 <b>-</b> 66  |

| 4.3.2   | CPU Operations                           | 4-66           |

| 4.3.2.1 | CPU Sequencing                           | 4 - 6 7        |

| 4.3.2.2 | Control Lines                            | 4-75           |

Page

ſ

Paragraph

| 4.3.3     | Programmable Translation Array (PTA) 4-7       | 0   |

|-----------|------------------------------------------------|-----|

| 4.3.3.1   | Programmable Translation Array Conponents 4-7  |     |

| 4.3.3.2   |                                                |     |

| 4.3.3.2   |                                                |     |

|           | Microinstructions                              |     |

| 4.3.5     | Microinstruction Bus Operation 4-10            |     |

| . 4.3.5.1 | Bus Operation                                  |     |

| 4.3.5.2   | Microinstruction Bus Element Description 4-10  |     |

| 4.3.5.3   | Data Chip                                      |     |

| 4.3.5.4   | Control Chip 4-1                               |     |

| 4.3.5.5   | Microinstruction ROM 4-1                       | 16  |

| 4.3.6     | Data Access 4-1                                | 17  |

| 4.3.6.1   | Input/Output Instructions 4-1                  | 18  |

| 4.3.6.2   | Data/Address Lines 4-1.                        | 34  |

| 4.3.6.3   | Control Lines 4-1.                             | 34  |

| 4.3.6.4   | Interrupt, Reset, and Compute 4-13             | 36  |

| 4.3.6.5   | Input/Output Operations 4-1                    | 37  |

| 4.4       | Círcuit Module Description 4-14                | 42  |

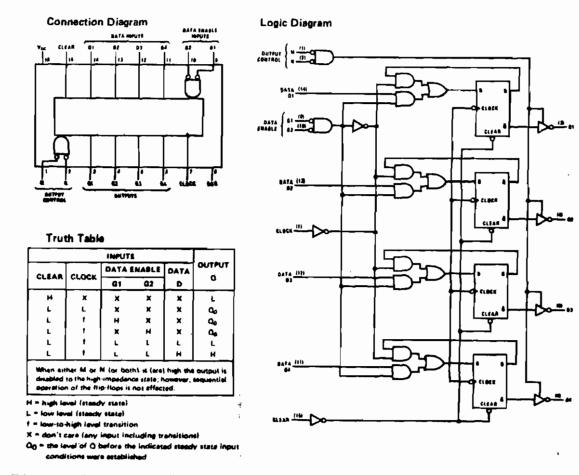

| 4.4.1     | Four-Phase Clock Generator (Board 2, U12) 4-14 | 43  |

| 4.4.2     | Tri-State 4-Bit D Type Register (Board 1,      |     |

|           | U1, U9, U10)                                   | 45  |

| 4.4.3     | High-Speed Hex Inverter (Board 1, U7) 4-14     | 46  |

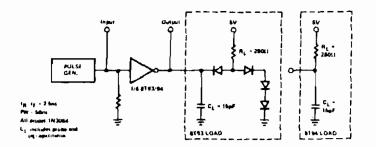

| 4.4.4     | Tri-State Buffers (Board 1, U5, U8, U22,       |     |

|           | U24, U26; Board 2, U45, U46, U48) 4-14         | 47  |

| 4.4.5     | Hex Tri-State Buffers (Board 2, Ull, U47) 4-14 | 48  |

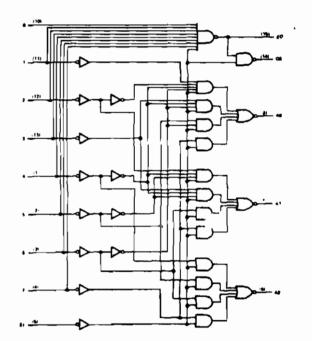

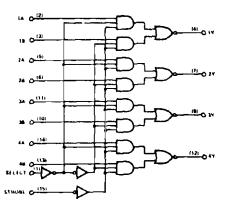

| 4.4.6     | Eight-Line to Three-Line Encoder (Board 2,     |     |

|           | U29, U30).                                     | 19  |

| 4.4.7     | Data Selector/Multiplexer (Board 1, U16,       |     |

| ·····     | U17, U18, U21)                                 | 50  |

| 4.4.8     | NAND TTL-to-MOS Driver Board (Board 1, U2;     | ,.  |

| 4.4.0     |                                                | 5 1 |

| 4 4 0     |                                                |     |

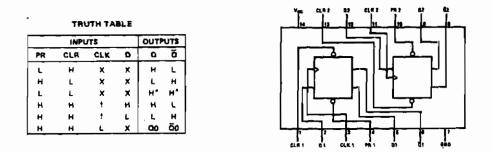

| 4.4.9     | D Positive-Edge-Triggered Flip-Flops with      |     |

|           | Preset and Clear (Board 2, U6, U18, U19,       | 52  |

|           | $U_{23}, U_{31}, U_{32}, U_{34}, U_{36})$      | 52  |

# Paragràph

| 4.4.10 | Dual J-K Negative-Edge-Triggered Flip-Flops |   |

|--------|---------------------------------------------|---|

|        | With Preset (Board 2, U10, U28, U40, U50,   |   |

|        | U51)                                        | 3 |

| 4.4.11 | Dual Retriggerable One-Shots With Clear     |   |

|        | (Board 2, U22)                              | 4 |

| 4.4.12 | Dual Voltage Controlled Oscillators (Board  |   |

|        | 2, U5)                                      | 5 |

| 4.4.13 | Decoder (Board 2, U7, U8, U42) 4-15         | 6 |

| 4.4.14 | D Flip-Flops With Clear (Board 1, U13, U14, |   |

|        | U25; Board 2, U10) 4-15                     | 7 |

| 4.4.15 | Tri-State Octal Buffers (Board 1, U6, U11,  |   |

|        | U19, U27)                                   | 8 |

|        | SECTION 5 MAINTENANCE AND TROUBLESHOOTING   |   |

| 5.0    | Introduction                                |   |

| 5.1    | Circuit Board Checkout 5-1                  |   |

| 5.2    | Warranty Procedures                         |   |

|        | SECTION 6 SCHEMATIC AND PARTS LIST          |   |

|        | Schematic and Parts List 6-1                |   |

`

Page

.

(

(

\*\*\*\*\*

# LIST OF ILLUSTRATIONS

.

# Figure

# Page

| 1-1    | AM-100 Circuit Board Set Simplified Block |              |

|--------|-------------------------------------------|--------------|

|        | Diagram                                   | 1 <b>-</b> 3 |

| 1-2    | AM-100 System Block Diagram               | 1-5          |

| 2-1    | Header Jumper Wiring                      | 2 - 7        |

| 2-2    | Real Time Clock Connection                | 2-10         |

| 4-1    | S-100 Bus Read Timing                     | 4 - 5        |

| 4 - 2  | S-100 Bus Write Timing                    | 4-6          |

| 4 - 3  | S-100 Bus Read-Modify-Write Timing        | 4-7          |

| 4 - 4  | S-100 Bus DMA Timing                      | 4 - 8        |

| 4 - 5  | CPU Chip Set                              | 4-17         |

| 4 - 6  | Microinstruction Bus Timing               | 4-20         |

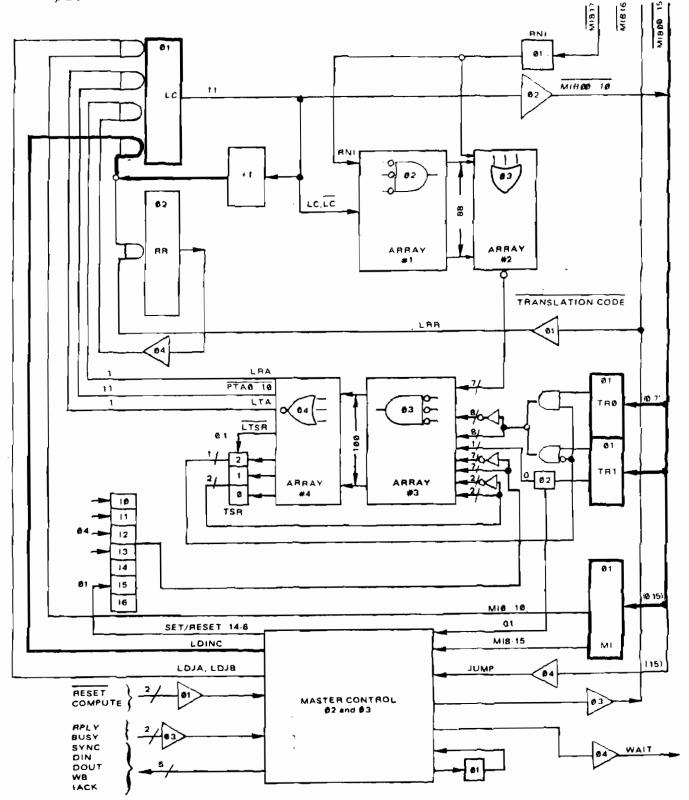

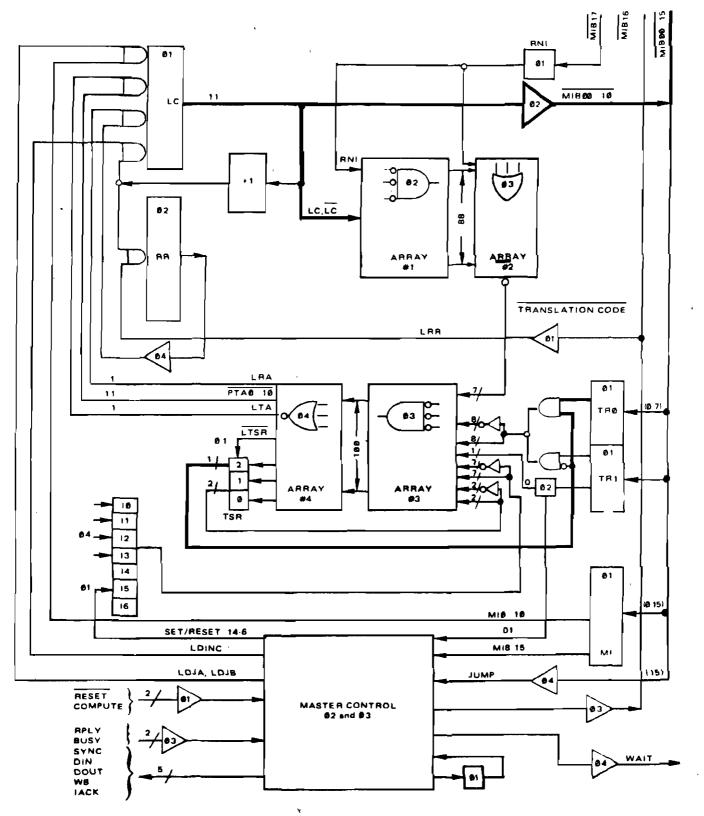

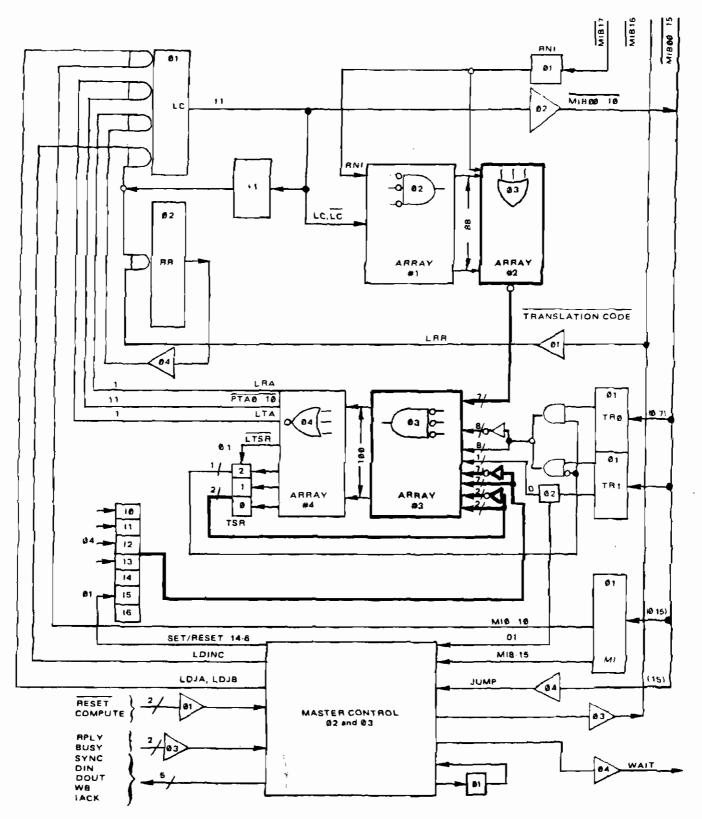

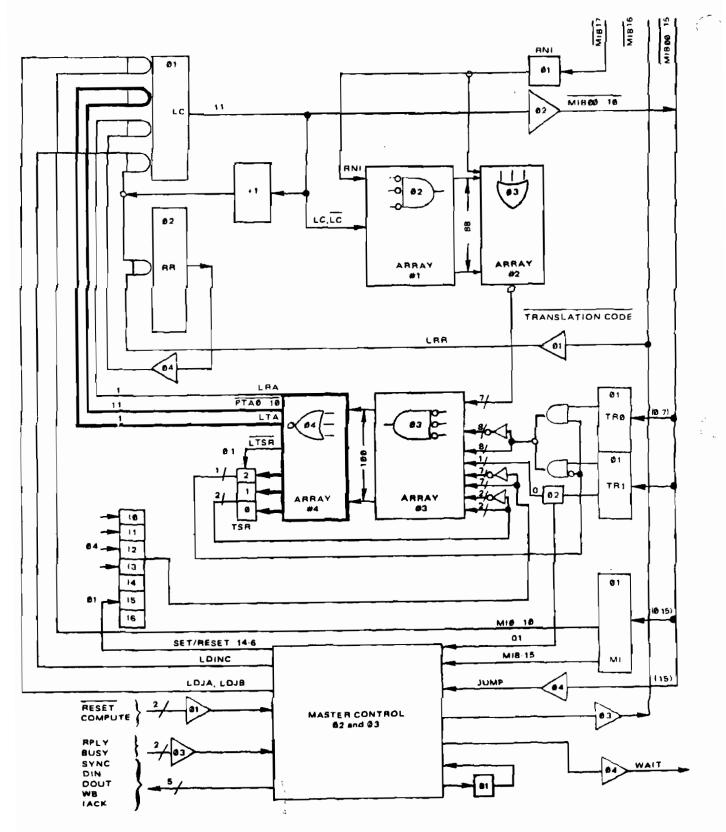

| 4 - 7  | AM-100 Functional Block Diagram           | 4-23         |

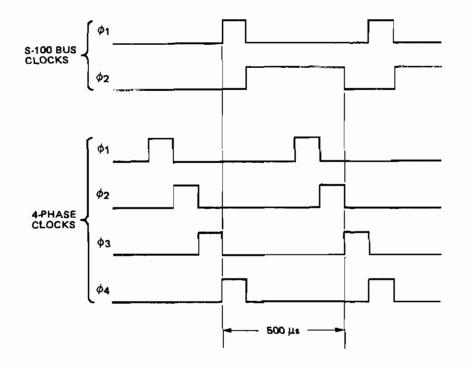

| 4 - 8  | AM-100 System Clocks                      | 4-34         |

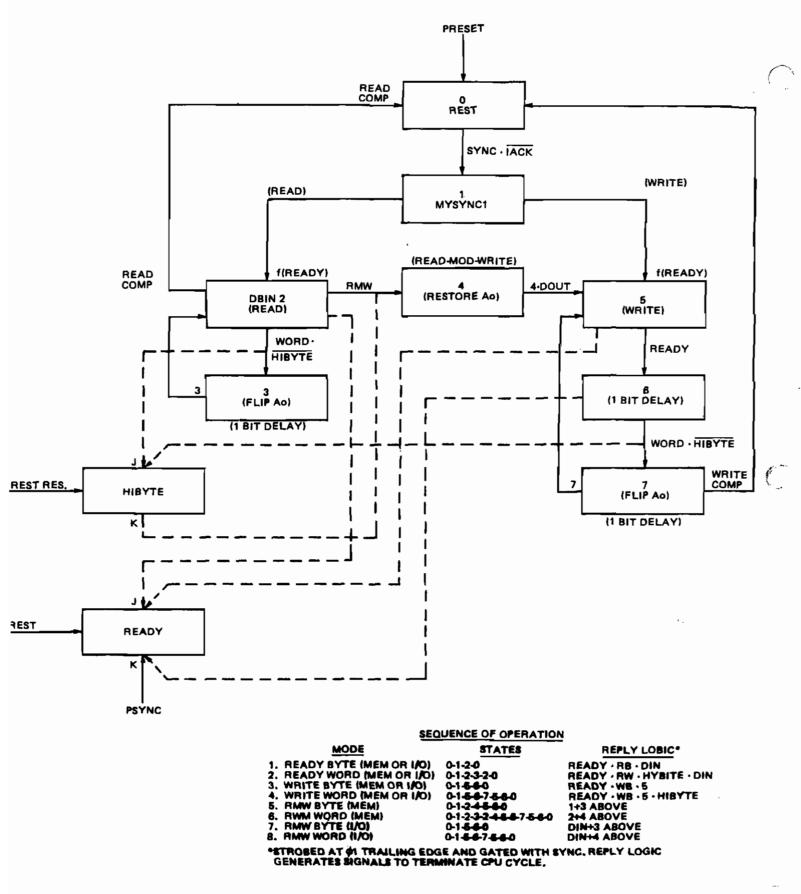

| 4 - 9  | Sequencer Flow Diagram                    | 4-39         |

| 4-10   | Sequencer Logic Equations                 | 4-40         |

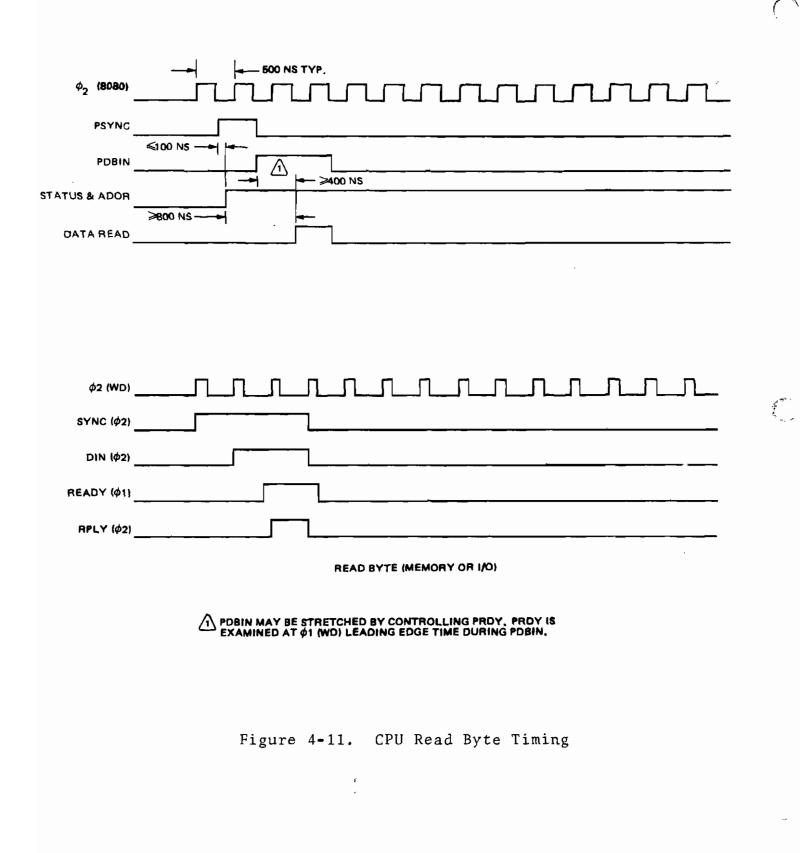

| 4-11   | CPU Read Byte Timing                      | 4-41         |

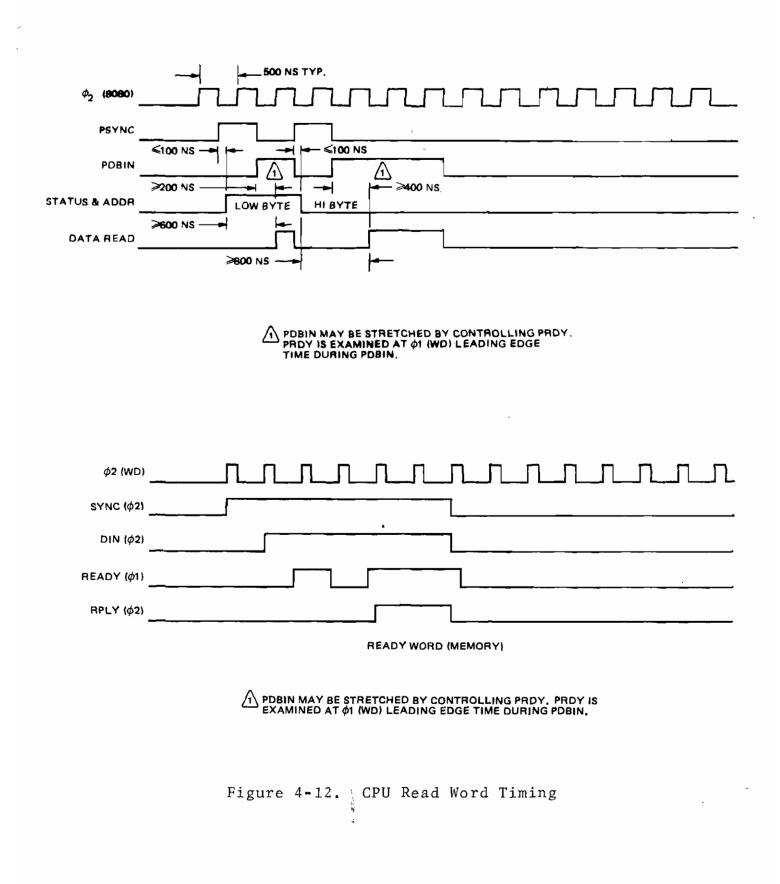

| 4-12   | CPU Read Word Timing                      | 4 - 42       |

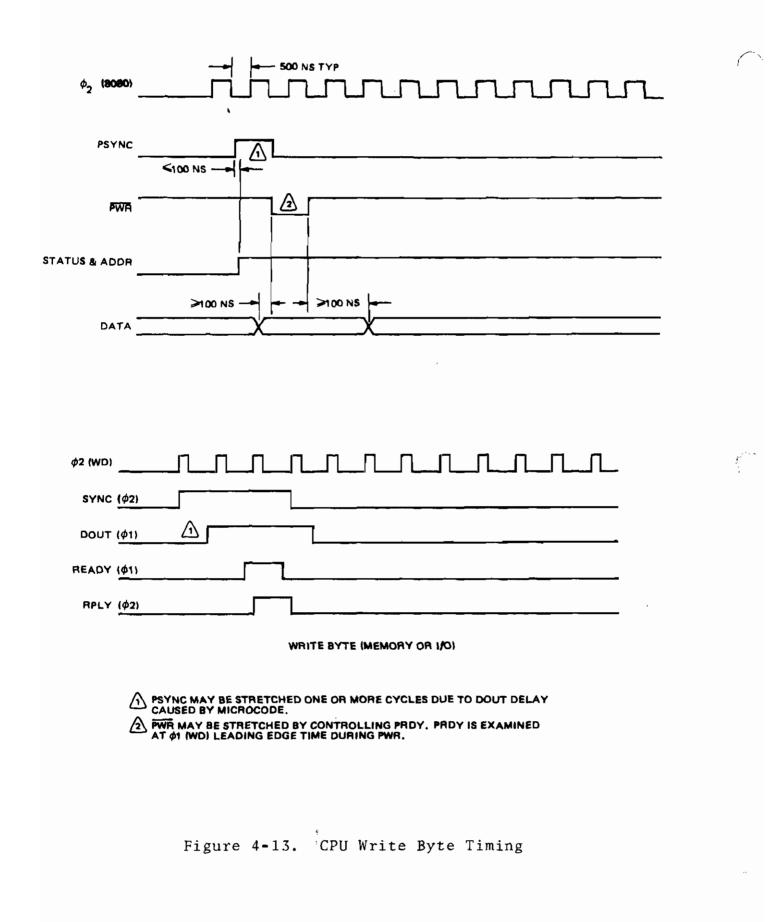

| 4 - 13 | CPU Write Byte Timing                     | 4-43         |

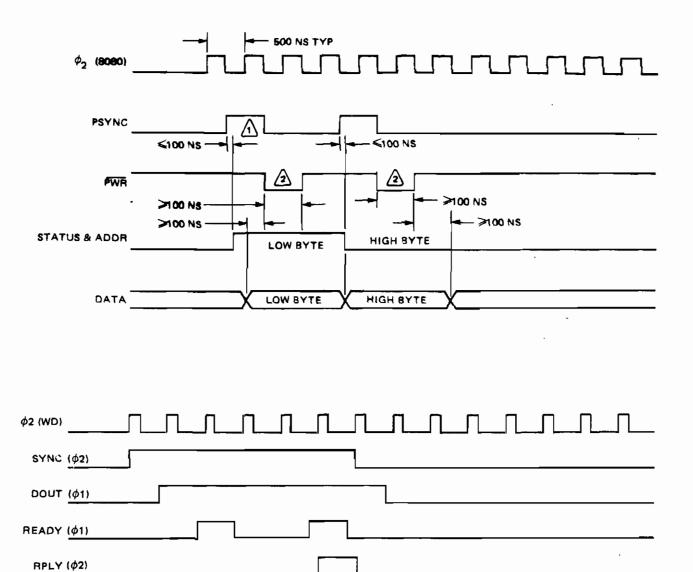

| 4-14   | CPU Write Word Timing                     | 4 - 44       |

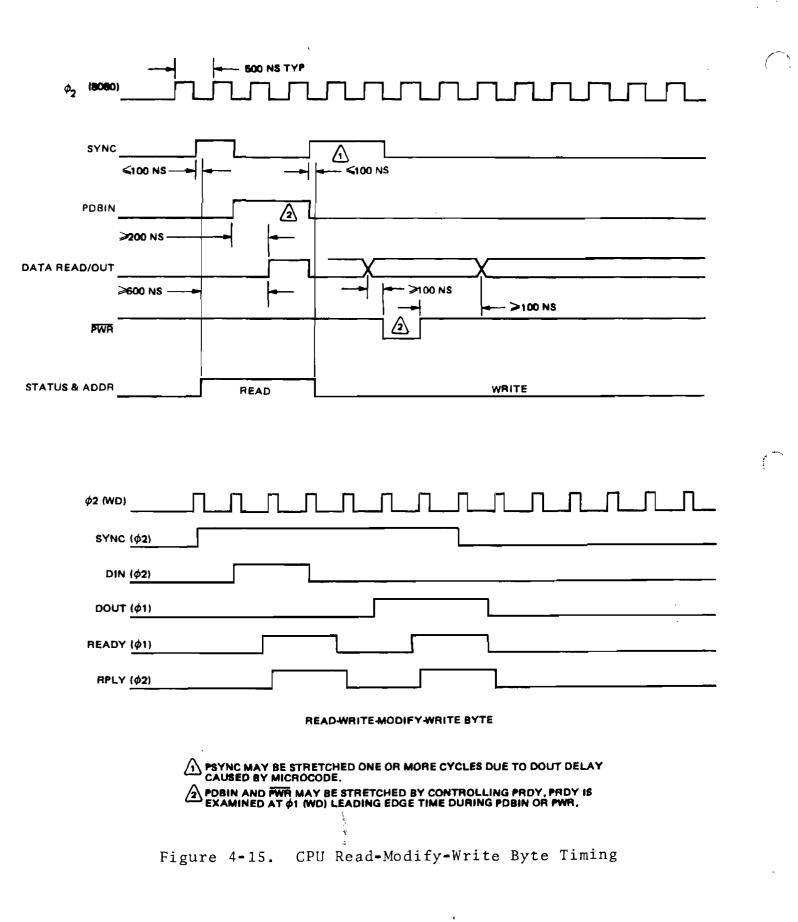

| 4-15   | CPU Read-Modify-Write Byte Timing         | 4-45         |

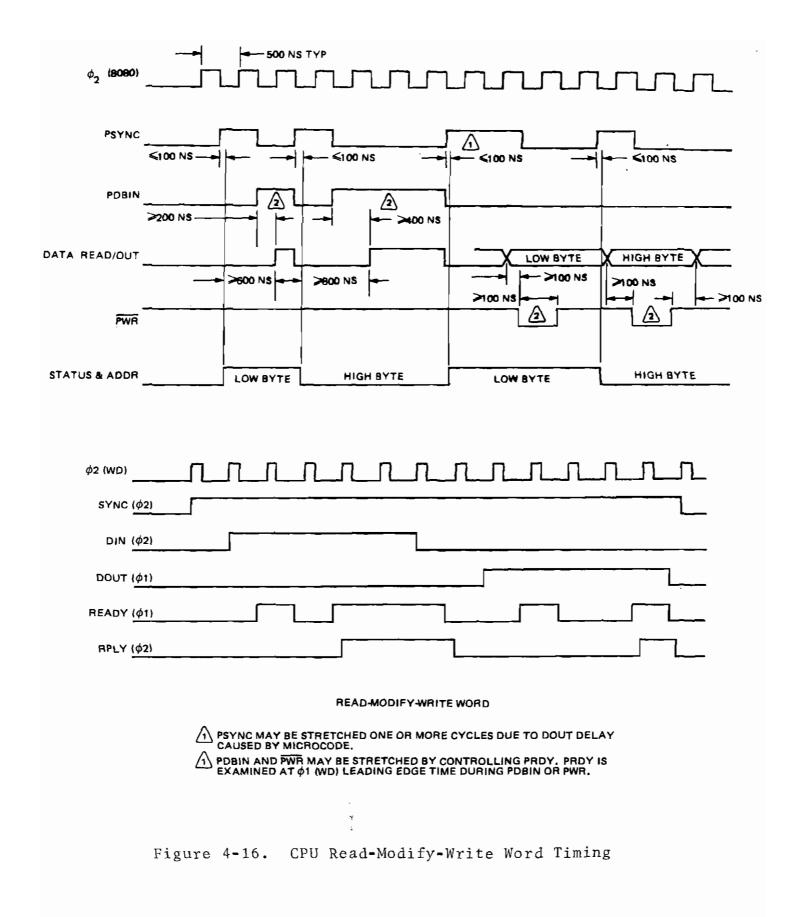

| 4-16   | CPU Read-Modify-Write Word Timing         | 4-46         |

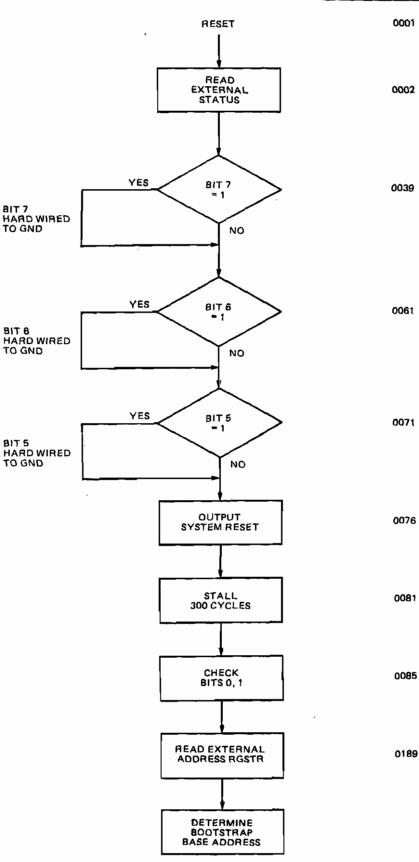

| 4-17   | AM-100 Power-Up Sequence                  | 4 - 49       |

| 4-18   | MCP 1600 Microprocessor Block Diagram     | 4-55         |

| 4-19   | Register File                             | 4-61         |

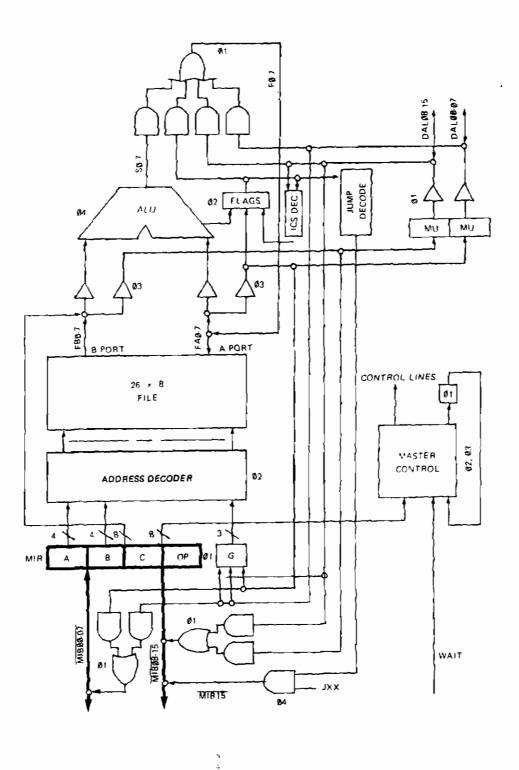

| 4-20   | Ø1 Data Paths                             | 4-70         |

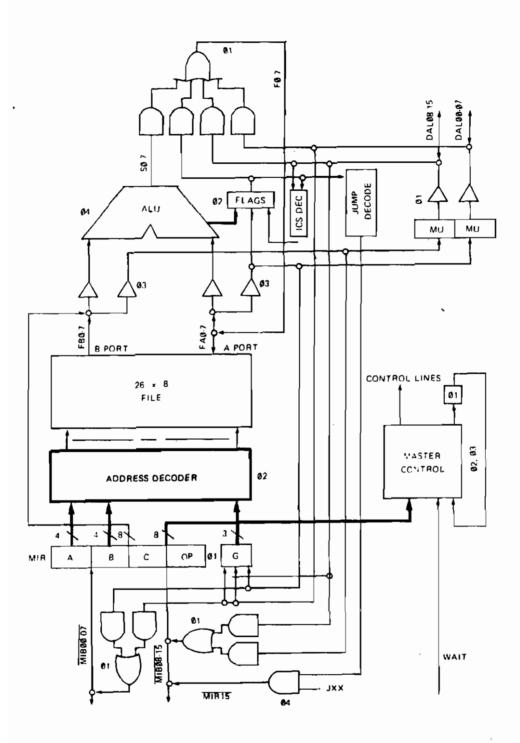

| 4 - 21 |                                           | 4-71         |

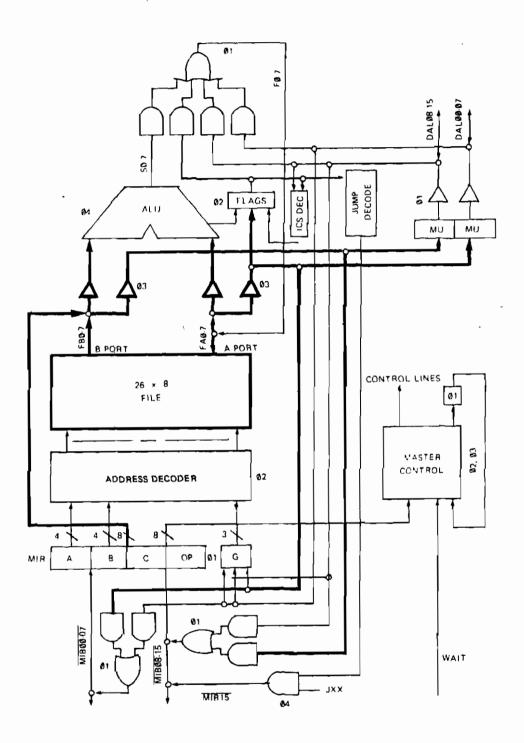

| 4 - 22 | Ø3 Data Paths                             | 4-72         |

Figure

.

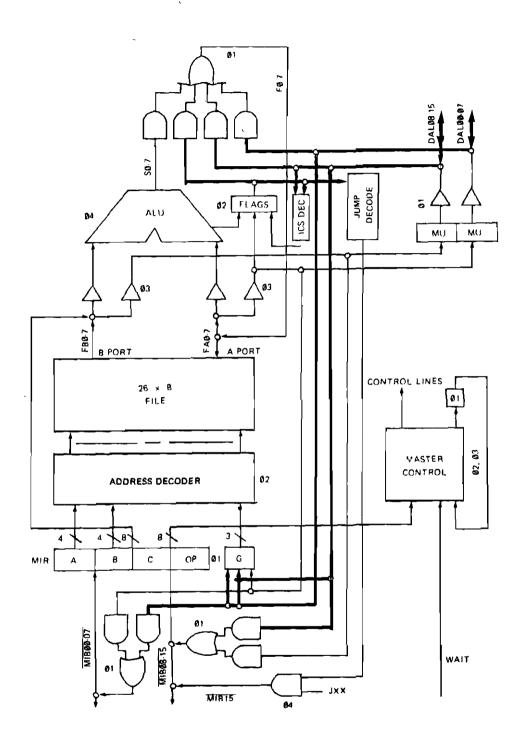

| 4-23          |                                                | 4-73           |

|---------------|------------------------------------------------|----------------|

| 4 - 24        |                                                | 4-74           |

| 4 - 25        | Major Control Lines                            | 4-76           |

| 4 - 26        | PTA Component Interconnections                 | 4-80           |

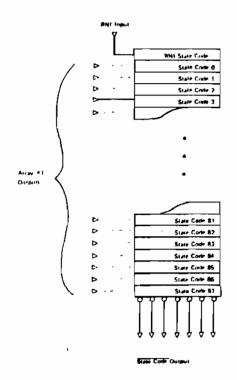

| 4 - 2 7       | Array No. 1 Organization                       | 4-81           |

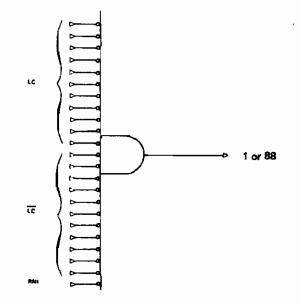

| 4 - 2 8       | Typical Gate - Array No. 1                     | 4-81           |

| 4-29          | Array No. 2 Data Specification                 | 4-82           |

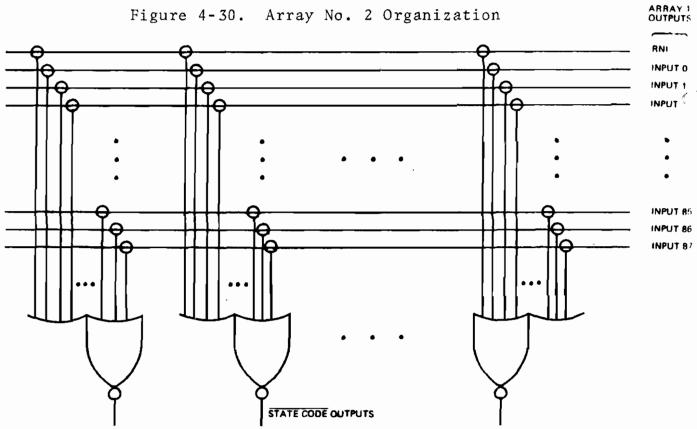

| 4 - 30        | Array No. 2 Organization                       | 4-83           |

| 4-31          | Array No. 2 Gate and Interconnect Structure    | 4-83           |

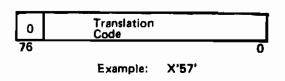

| 4-32          | Data Specification                             | 4-85           |

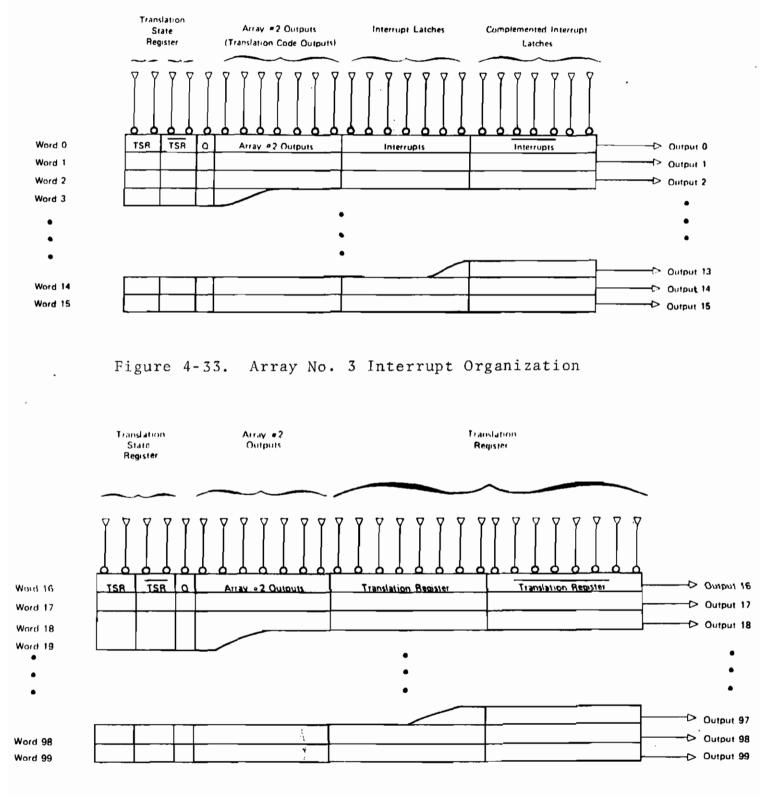

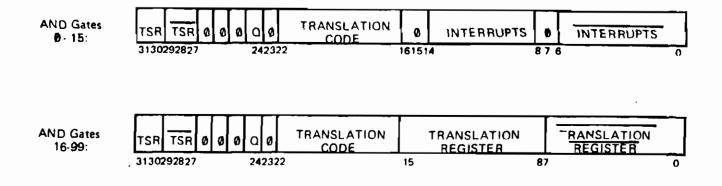

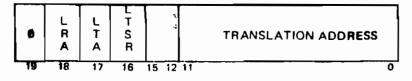

| 4 - 33        | Array No. 3 Interrupt Organization             | 4-86           |

| 4 - 34        | Array No. 3 Translation Register Organization. | 4-86           |

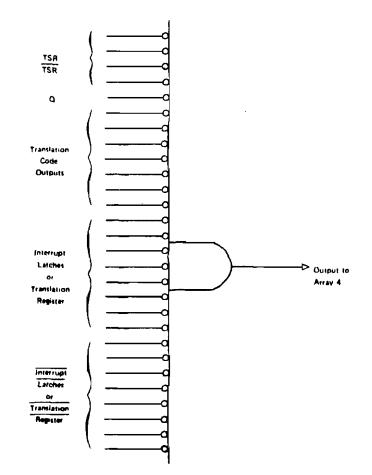

| 4 - 35        | Typical Gate of Array No. 3                    | 4-87           |

| 4 - 36        | Array No. 4 Organization                       | 4-89           |

| 4 - 37        | Ø1 Data Flow                                   | 4 - 9 2        |

| 4 - 38        | Ø2 Data Flow                                   | 4-93           |

| 4 - 39        | Ø3 Data Flow                                   | 4-94           |

| 4 - 40        | Ø4 Data Flow                                   | 4 <b>-</b> 9 5 |

| 4 - 41        | System Interconnections Microprocessor Set     | 4-108          |

| 4 - 4 2       | TTL Output Timing CP1631B                      | 4-113          |

| 4 - 4 3       | Microinstruction Bus Interface Timing          | 4-115          |

| 4 - 44        | Control Chip Microinstruction Bus Timing       | 4-116          |

| 4 - 4 5       | Microinstruction Bus Timing CP1631B            | 4-117          |

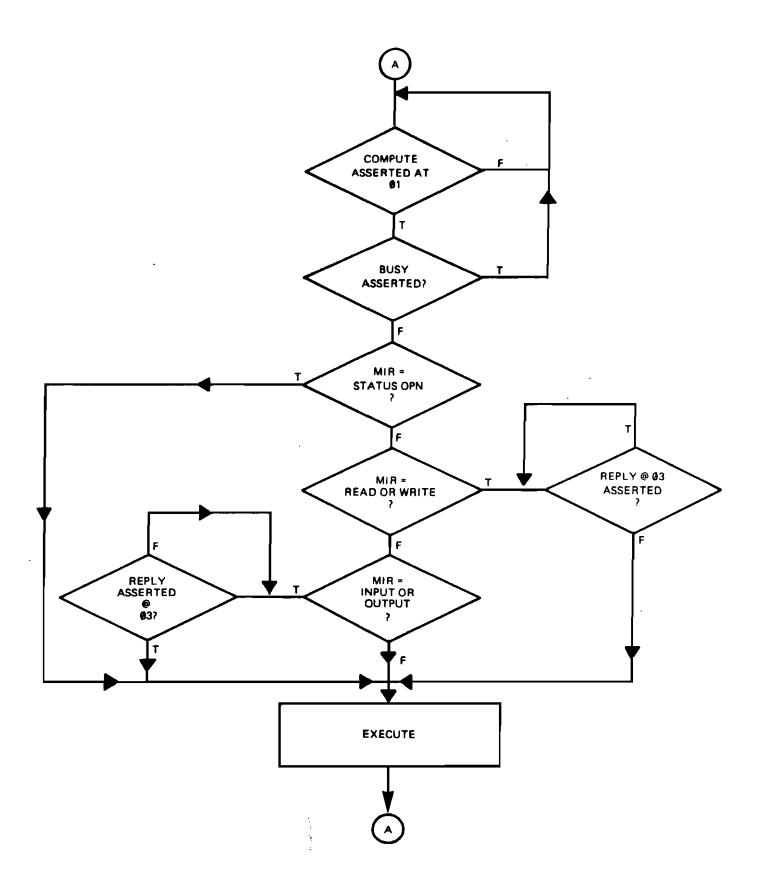

| 4-46          | I/O Instruction Condition Testing              | 4-120          |

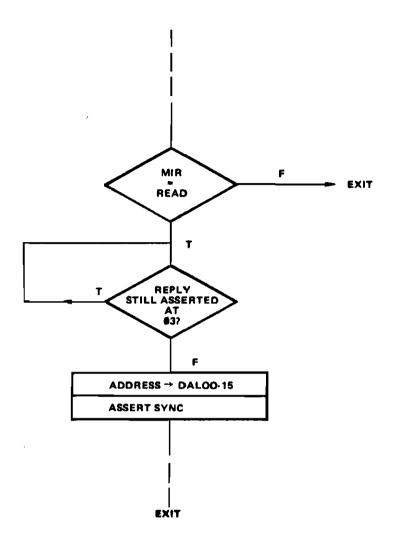

| 4 - 4 7       | Execution of Read Instruction                  | 4-121          |

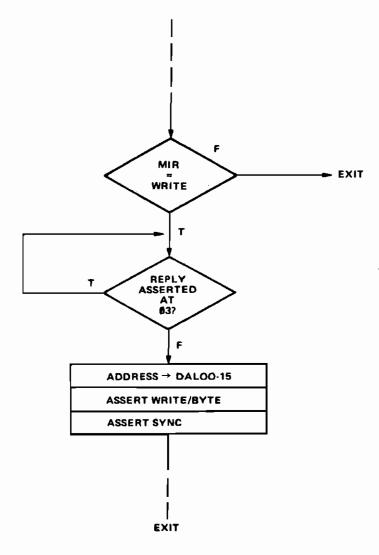

| 4 - 48        | Execution of Write Instruction                 | 4-124          |

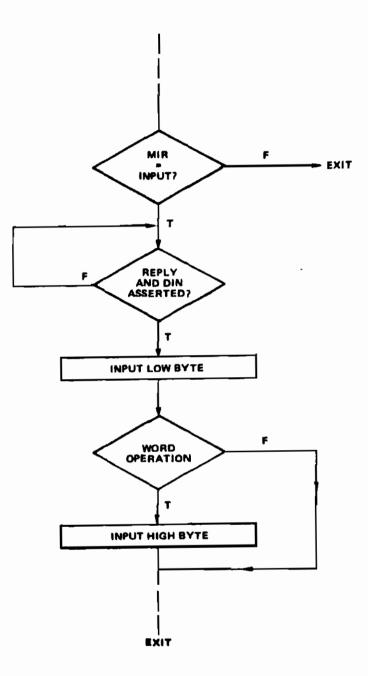

| 4-49          | Execution of Input Instruction                 | 4-128          |

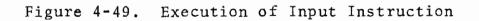

| 4 <b>-</b> 50 | Execution of Output Instruction                | 4-131          |

| 4-51          | Write/Output Sequence                          | 4-139          |

| 4 - 52        | Read/Input Sequence                            | 4-139          |

| 4 - 5 3       | Read-Modify-Write Sequence                     | 4-140          |

| 4 - 54        | Interrupt Acknowledge Sequence                 | 4-141          |

|               |                                                |                |

# Figure

4,8

.

.

| 4 <b>-</b> 5 5 | Four Phase Clock Logic and Timing              | 4-144          |

|----------------|------------------------------------------------|----------------|

| 4-56           | Tri-State 4-Bit D Type Register Connections    | 4-145          |

| 4 - 57         | High Speed Hex Inverter Connections            | 4-146          |

| 4 - 58         | Tri-State Buffer Connections                   | 4-147          |

| 4-59           | Hex Tri-State Buffer Connections               | 4-148          |

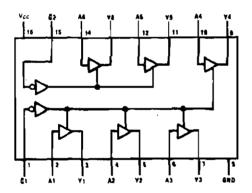

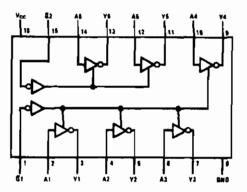

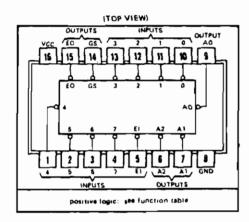

| 4-60           | Eight-Line to Three-Line Encoder Connections . | 4 <b>-</b> 149 |

| 4-61           | Data Selector/Multiplexer Connections          | 4-150          |

| 4-62           | NAND TTL-To-MOS Driver Connections             | 4-151          |

| 4-63           | D Flip-Flop Connections                        | 4 <b>-</b> 152 |

| 4-64           | J-K Flip-Flop Connections                      | 4-153          |

| 4-65           | One-Shot Connections                           | 4-154          |

| 4 <b>-</b> 66  | Dual Voltage Controlled Oscillator Connections | 4-155          |

| 4-67           | Decoder Connections                            | 4-156          |

| 4-68           | D Flip-Flop Connections                        | 4-157          |

| 4-69           | Tri-State Octal Buffer Connections             | 4-158          |

. 1

# LIST OF TABLES

,

Table

Page

| 2-1     | AM-100 Specifications                  | ٠  | •   | • • | 2-1            |

|---------|----------------------------------------|----|-----|-----|----------------|

| 2 - 2   | AM-100 Interface Signals               | •  | •   | • • | 2-3            |

| 3-1     | Alpha Micro I/O Addresses              | •  | •   |     | 3-2            |

| 3-2     | Boot Addresses                         | •  | •   | • • | 3-3            |

| 3-3     | DMA Levels                             | •  | •   | • • | 3-4            |

| 3-4     | Interrupt Levels                       |    |     |     | 3-4            |

| 4~1     | S-100 Bus Command/Control Lines        | •  | •   |     | 4-3            |

| 4 - 2   | S-100 Bus Status Lines                 | •  | •   | • • | 4-3            |

| 4 - 3   | S-100 Bus Utility Lines                | •  | •   | • • | 4-3            |

| 4 - 4   | S-100 Bus Interface Signals List       | •  | • • | • • | 4-10           |

| 4 - 5   | AM-100 Signals List                    | •  | •   | • • | <b>4 -</b> 2 7 |

| 4-6     | Microm State Code Functions            |    | •   | • • | 4 <b>-</b> 36  |

| 4 - 7   | Status Byte Buffer Bits                |    | •   |     | 4 - 47         |

| 4 - 8   | CPU Chip Set Interrupts                | •  | • • | •   | 4 - 52         |

| 4 - 9   | Data Chip (CP1611B) Pin Assignments .  |    | • • |     | 4-56           |

| 4-10    | Control Chip (CP1621B) Pin Assignments | •  | • • |     | 4 - 5 7        |

| 4-11    | Microm Chip (CP1631B) Pin Assignments  |    | • • |     | 4-57           |

| 4-12    | Translation State Code Outputs 4 of    | 7  | • • | •   | 4 - 84         |

| 4 - 1 3 | Translation State Code Outputs 5 of    | 7  | • • | •   | 4 - 84         |

| 4-14    | Microinstruction Set                   | •  | • • | •   | 4 <b>-</b> 99  |

| 4-15    | Microinstructions                      | •  | • • | •   | 4-100          |

| 4-16    | Summary of Microinstruction and Status | F1 | ags | ; . | 4-105          |

| 4-17    | Microbus Timing                        | •  | •   |     | 4-110          |

|         |                                        |    |     |     |                |

ъ ;

# SECTION 1 GENERAL DESCRIPTION

## 1.0 INTRODUCTION.

This manual provides operating and maintenance instructions for the AM-100 Central Processor Unit (CPU) circuit board set manufactured by Alpha Microsystems located in Irvine, California. Circuit board description, operating and usage instructions, programming, theory of operation, and maintenance instructions are included to provide the user with the information necessary to utilize this circuit board to its full capability.

#### 1.1 CIRCUIT BOARD DESCRIPTION.

The AM-100 CPU circuit board set is a 16-bit microprocessor board set that is compatible with the S-100 Bus structure. The AM-100 utilizes the Western Digital WD16 chip set microprogrammed to enhance the software of the operating system. The microprocessor provides 16-bit flexibility and speed with floating point arithmetic to provide large throughput. The two board AM-100 supports most of the standard S-100 Bus peripherals including static memory, I/O facilities and video.

A simplified block diagram of the AM-100 CPU board set is shown in Figure 1-1. For a complete detailed description of CPU operation, see Section 4 of this manual.

## 1.2 APPLICATION.

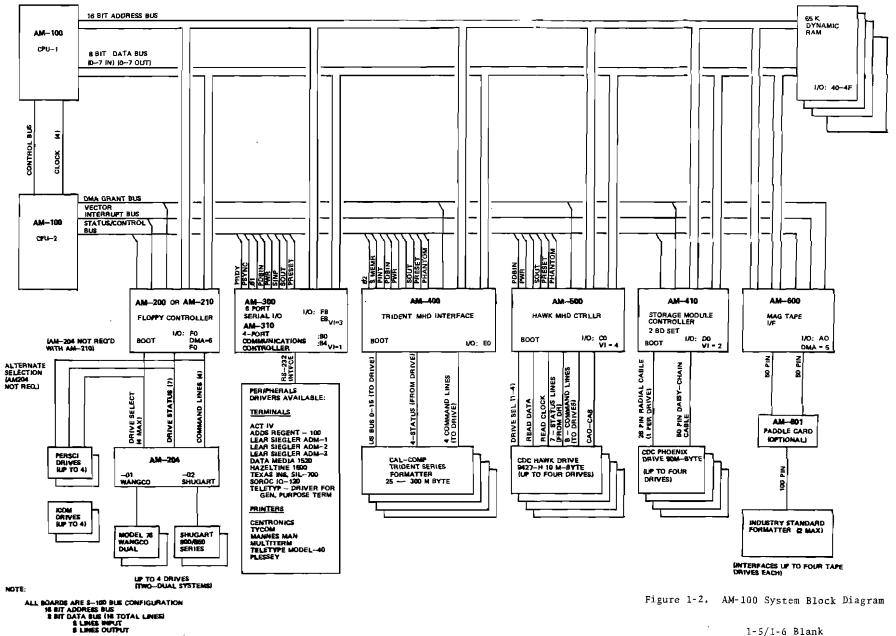

The AM-100 is a 16-bit CPU that is fully compatible with a standard 8-bit S-100 bus system. It is fully compatible with many available peripherals from other manufacturers. A block diagram of the system capability is contained in Figure 1-2. This shows the basic S-100 Bus structure, the currently available Alpha Micro circuit cards, and the commercially available peripherals that can be used for a fully integrated system.

1-5/1-6 Blank

Figure 1-1. AM-100 Simplified Block Diagram

1-3/1-4 Blank

# SECTION 2 OPERATING DATA

2.0 INTRODUCTION.

This Section contains information on the use of the AM-100 CPU two board set. Capabilities, specifications, interface wiring and user option descriptions are provided for the successful integration of the board into the user's system.

2.1 CAPABILITIES AND SPECIFICATIONS.

This two board set operates from the standard S-100 Bus structure and can be integrated into a complete system. Specifications for the AM-100 are contained in Table 2-1.

| PARAMETER                | SPECIFICATION                                                                                                                                                    |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface type           | Standard S-100 Bus, 16-Bit words,<br>byte multiplexed for compatibility<br>to 8-bit peripherals and memories.                                                    |

| Instruction Set          | Over 150 standard instructions coded<br>in unique microcode executed on the<br>WD-16 CPU chip set.                                                               |

| Arithmetic<br>Operations | Hardware floating point arithmetic to 11 significant digits.                                                                                                     |

| CPU Architecture         | Microprogrammed instruction set;<br>eight 16-bit general purpose regis-<br>ters; floating point hardware unit;<br>special high-speed byte multiplexing<br>logic. |

Table 2-1. AM-100 Specifications

| Table | 2-1 | (Cont.). | AM-100 | Specifications |

|-------|-----|----------|--------|----------------|

|-------|-----|----------|--------|----------------|

| PARAMETER            | SPECIFICATION                                                         |

|----------------------|-----------------------------------------------------------------------|

| Interrupt Capability | Eight vectored and one non-vectored interrupt lines.                  |

| DMA Capability       | Seven DMA channels. (Included in vec-<br>tored interrupt line count.) |

| Real Time Clock      | Standard Feature.                                                     |

| Circuit Boards       | Two board set - standard 5" x 10"<br>with 100-pin connectors.         |

2.2 INTERFACE DESCRIPTION AND WIRING.

The AM-100 CPU interfaces with the standard S-100 Bus structure. All data inputs, outputs, and control signals are transferred through these lines. The S-100 bus connections are made by the bottom edge connectors and are listed in Table 2-2.

| SIGNAL | NAME           | J1<br>PIN NO. |

|--------|----------------|---------------|

| A0     | Address 0      | 79            |

| A1     | Address 1      | 80            |

| A2     | Address 2      | 81            |

| A 3    | Address 3      | 31            |

| A4     | Address 4      | . 30          |

| A 5    | Address 5      | 29            |

| A6     | Address 6      | 82            |

| A 7    | Address 7      | 83            |

| A 8    | Address 8      | 84            |

| A9     | Address 9      | 34            |

| A10    | Address 10     | 37            |

| A11    | Address 11     | 87            |

| A12    | Address 12     | 33            |

| A13    | Address 13     | 85            |

| A14    | Address 14     | 86            |

| A15    | Address 15     | 32            |

| CLOC   | 2 MHz Clock    | 49            |

| DIO    | Data Input Bus | 95            |

| DI1    | Bits 0-7       | 94            |

| DI2    |                | 41            |

| DI3    |                | 42            |

| DI4    |                | 91            |

| DI5    |                | 92            |

| DIG    |                | 93            |

| DI7    |                | 4 3           |

Table 2-2. AM-100 Interface Signals

.

. . . . . . . . . . . . . . .

r

# Table 2-2 (Cont.). AM-100 Interface Signals

L.3

| SIGNAL                                                                       | NAME                     | J1<br>PIN NO.                                |

|------------------------------------------------------------------------------|--------------------------|----------------------------------------------|

| DMAGRO<br>DMAGR1<br>DMAGR2<br>DMAGR3<br>DMAGR4<br>DMAGR5<br>DMAGR6<br>DMAGR7 | DMA Grant                | 63<br>62<br>61<br>60<br>59<br>58<br>57<br>56 |

| DMARCVD                                                                      | DMA Received             | 64                                           |

| D00<br>D01<br>D02<br>D03<br>D04<br>D05<br>D06<br>D07                         | Data Out Bus<br>Bits 0-7 | 36<br>35<br>88<br>89<br>38<br>39<br>40<br>90 |

| C/CDSB<br>ADDDSB<br>DODSB                                                    | Not Used                 | 18<br>19<br>22                               |

| MWRITE                                                                       | Memory Write             | 68                                           |

| PDBIN                                                                        | Data Bus In              | 78                                           |

| PHLDA                                                                        | P-Hold Acknowledge       | 26                                           |

2-4

4

# Table 2-2 (Cont.). AM-100 Interface Signals

.

ر: ``

.

| SIGNAL | NAME                     | J1<br>PIN NO. |

|--------|--------------------------|---------------|

| PHOLD  | DMA Request Line         | 74            |

| PINTE  | CPU Interrupt Enable     | 28            |

| POC    | Power On Clear           | 99            |

| PRESET | Preset                   | 75            |

| PSYNC  | Processor Sync           | 76            |

| PWAIT  | CPU Wait                 | 27            |

| PWR    | Write Strobe             | 77            |

| SINP   | I/O Input Cycle          | 46            |

| SINTA  | Interrupt Acknowledge    | 96            |

| SMEMR  | Memory Read Cycle        | 47            |

| SM1    | Bus Master OP Code Fetch | 44            |

| SOUT   | I/O Output Cycle         | 45            |

| SWO    | Bus Master Output        | 97            |

Table 2-2 (Cont.). AM-100 Interface Signals

| SIGNAL                                                                                                | NAME                                                                                                                                                                                         | J1<br>PIN NO.                          |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VI0           VI1           VI2           VI3           VI4           VI5           VI6           VI7 | Vectored Interrupt 0<br>Vectored Interrupt 1<br>Vectored Interrupt 2<br>Vectored Interrupt 3<br>Vectored Interrupt 4<br>Vectored Interrupt 5<br>Vectored Interrupt 6<br>Vectored Interrupt 7 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 |

| STVAL<br>Ø2                                                                                           | Status and Address Valid<br>Phase 2 Clock                                                                                                                                                    | 25<br>24                               |

## 2.3 USER OPTIONS.

Most of the optional capabilities of the AM-100 CPU are exercised with software, and an overview of the available software capability is contained in Section 3. The hardware option that must be implemented is for the bootstrap Loader program and determines which peripheral the boot loader is accessed from.

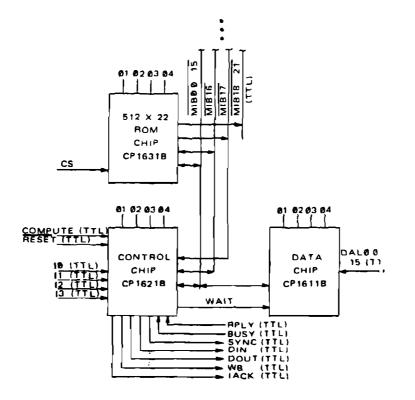

The boot loader may be accessed from either the AM-200 circuit board (floppy disk controller), the AM-500 (hard disk controller) or the AM-400 (hard disk interface). Header U3 selects the base address for the boot program by the jumper wires as shown in Figure 2-1. CPU1 Header U3

AM-200 Floppy Disk or AM-400 Trident Disk AM-500 (Hawk) Hard Disk

Figure 2-1. Header Jumper Wiring

Header U3 on CPU1 can be jumpered for other non-standard jump addresses. The address lines that are jumper selectable are A8-A13 with A14 and A15 always high (1).

To select an address, pins 3, 4, 5, 6, 7 and 8 can be jumpered to ground or left open to generate the desired code. An open (no jumper) selects a one for that address bit and a jumper to pin 14 selects a zero.

NOTE

Pins 9, 10, 11, 12, 13 and 14 on header U3 must always be connected together.

The pins on header that correspond to the various address bits are as follows:

| Address line | <u>Pin on U3</u> |

|--------------|------------------|

| 8            | 5                |

| 9            | 4                |

| 10           | 7                |

| 11           | 3                |

| 12           | 8                |

| 13           | б                |

| GND          | 14               |

### 2.4 INTERRUPT AND DMA OPTIONS.

The AM-100 provides seven levels of DMA or eight levels of interrupt capability. The interrupt and DMA signal lines to the S-100 bus are user selected with jumper wires applied to the circuit board. These jumpers select the desired vectored interrupts or DMA grant signals.

### 2.5 SYSTEM CONNECTIONS.

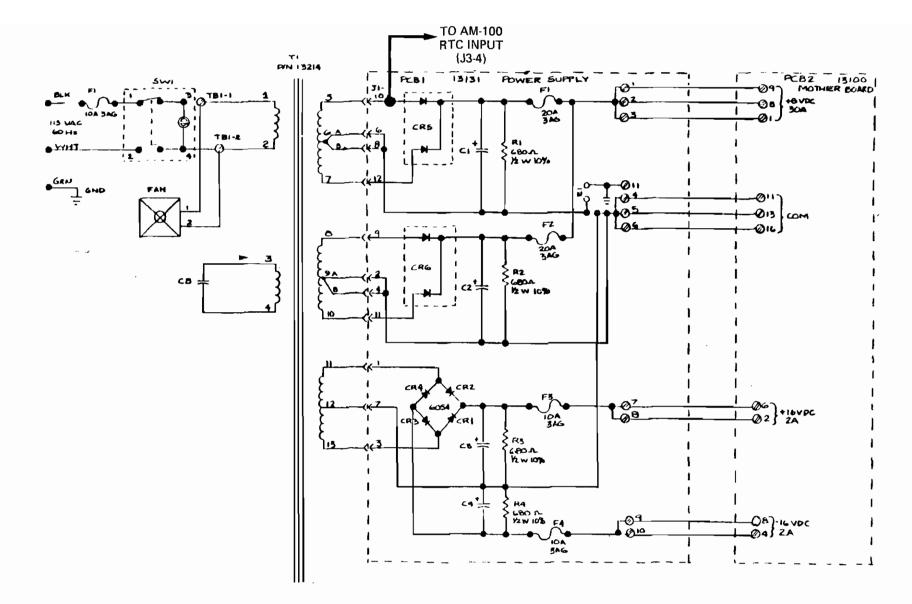

The AM-100 board set plugs into two adjacent slots in a S-100 Bus chassis and are connected together by a 40 pin flat cable along the top of the circuit boards. An additional input must be connected to the real time clock of the CPU. This can be supplied from the 50 or 60 Hz power of the low voltage power supply in the S-100 bus chassis. Connect this 50 or 60 Hz signal to CPU board 2 at header U3 pin 12 according to the following procedure as shown in Figure 2-2. The AM-100 is then ready for use.

- 1. Make sure AC power is off and chassis is unplugged.

- Locate the secondary transformer tap supplying the +8 volt rectifier. The accompanying schematic illustrates this point for the TEI MCS-122 chassis.

- 3. Locate the E-Z hook cable supplied with the AM-100 CPU board set.

- 4. Cut one end off the cable so that it is long enough to reach from the top of the AM-100 CPU set to the transformer tap connection located in Step 2. (Make sure that the cable is long enough to be conveniently routed.)

- 5. Solder the cut end of the cable to the transformer tap connection.

- 6. Before attaching the cable to the AM-100, perform the following steps:

- a. Plug in the chassis and turn on AC power.

- b. Observe the waveform at the "E-Z" hook contact. It should appear as a  $\pm$  10 volt signal at 60 or 50 Hz.

- 7. If the waveform at Step 6b appears correct, turn off AC power, attach the "E-Z" hook to CPU board #2 at J3 pin 4. An extended resistor lead is provided for convenience in hook-up.

Figure 2-2. Real Time Clock Connection

## SECTION 3 PROGRAMMING

3.0 INTRODUCTION.

This section provides information for programming the AM-100 CPU and integrating it into the user's system. The actual software itself is not contained in this manual. Only the requirements and descriptions of the available software programs and their capabilities are presented here.

3.1 SYSTEM CONFIGURATION.

A minimum system can consist of the AM-100 two board set, a minimum of 32K bytes of memory on a S-100 Bus memory board, a serial I/O card such as the AM-300, a disk memory, and a terminal. A PROM is needed to bootstrap the system and this can be located on one of the peripheral interface boards. Other standard Alpha Micro devices include:

- 1. Floppy disk subsystem (AM-200/AM-210).

- 2. Ten megabyte hard disk (AM-500).

- 3. Large storage capacity hard disk (AM-400/AM-410).

- 4. Tape storage subsystem (AM-600).

To utilize other devices in the system, it is necessary to write a driver program for the device and place the resulting module in a preassigned disk area. The bootstrap PROM can be located on either the floppy controller interface board (AM-200) or the hard disk controller interface board (AM-500 or AM-400). The starting address for the bootstrap program is jumper selectable on a platform header on CPU Board 1, U3.

The standard addresses used in Alpha Micro systems are listed in Table 3-1 and boot addresses are listed in Table 3-2. The standard DMA levels are listed in Table 3-4 and the standard interrupt levels are listed in Table 3-5. For further details on interfacing Alpha Micro circuit boards, consult the Technical manual for the individual board.

| Table | 3-1. | Alpha | Micro | I/0 | Addresses |

|-------|------|-------|-------|-----|-----------|

|-------|------|-------|-------|-----|-----------|

۰,

| Address (Hex) | Interface                                                        |

|---------------|------------------------------------------------------------------|

| 00 - 0F       | Reserved                                                         |

| 10 - 3B       | Unassigned                                                       |

| 3C - 3F       | Reserved                                                         |

| 40 - 4F       | Memory Bank Switching (1 port/memory bd)                         |

| 50 ~ 6F       | Unassigned                                                       |

| 70 - 7F       | Phone Link (DC Hayes bd)                                         |

| 80 - 83       | Imsai PIO (parallel port, Data I/O control, etc.)                |

| 84 - 9F       | Unassigned                                                       |

| A0 - A7       | AM-600 Mag Tape I/F                                              |

| A8 - AF       | Unassigned                                                       |

| B0 - BF       | AM-310 4 Port Communications Bd (4 ports required/bd)            |

| C0 - C7       | ICOM Floppy Controller or AM-500 Disk Controller<br>(4 ports/bd) |

| C8 - CF       | Unassigned                                                       |

| C 2           | Unassigned                                                       |

.

Table 3-1 (Cont.). Alpha Micro I/O Addresses

| Address (Hex) | Interface                                               |

|---------------|---------------------------------------------------------|

| D0 - D3       | AM-410 Disk Controller                                  |

| D4 - DF       | Unassigned                                              |

| E0 - E7       | AM-400 Trident Formatter I/F                            |

| E8 - EF       | AM-300 Alternate (2nd board)                            |

| F0 - F7       | AM-200 Floppy Controller or AM-210 Floppy<br>Controller |

| F8 - FF       | AM-300 6 Port Serial I/O Board                          |

Table 3-2. Boot Addresses

| Address (Hex) | Boot Location                                                     |

|---------------|-------------------------------------------------------------------|

| F400          | AM-500 Boot Address<br>AM-410 Boot Address                        |

| FC00          | AM-200 Boot Address<br>AM-210 Boot Address<br>AM-400 Boot address |

| C000          | ICOM Floppy Boot Address                                          |

# TABLE 3-3. DMA Levels

| Level | Device                     |

|-------|----------------------------|

| 0     |                            |

| 1     |                            |

| 2     |                            |

| 3     |                            |

| 4     |                            |

| 5     | AM-600 Mag Tape Controller |

| 6     | AM-200 Floppy Controller   |

| 7     |                            |

# Table 3-4. Interrupt Levels

ť.

| Level  | Device                             |

|--------|------------------------------------|

| 0      |                                    |

| 1      | AM-310 4 Port Communications Board |

| 2      | AM-410 Disk Controller             |

| 3      | AM-300 6 Port Serial I/O           |

| 4      | AM-500 Disk Controller             |

| 5<br>6 | Not available on old systems       |

| 7      |                                    |

### 3.2 SOFTWARE OVERVIEW.

( ···

A wide variety of software programs are available for use in the AM-100 system that have been operating in the commercial environment for many years. These programs have been written under copyright solely by Alpha Microsystems ' and are available in either floppy disk or hard disk form.

### 3.2.1 OPERATING SYSTEM.

The operating system is a commercial, full multi-tasking, timesharing system capable of supporting as many job partitions as memory capacity will allow. Each job may be controlled by its own terminal or several jobs may be controlled by the same user terminal under a unique software control system built into the monitor. One job may also control several terminals. The status of each job may be optionally displayed on a central video display interfaced through a controller.

The I/O structure is fully device independent and contained within the monitor. To incorporate a new device into the system, the user creates a software driver to interface to the device and includes it in the monitor.

The terminal service routines are also device independent and operate through terminal drivers. Each terminal driver contains a software translation routine to allow the use of special terminal functions such as cursor address and common I/O routines to all types of terminals, without being dependent on which brand of terminal is attached to the system.

3.2.2 ASSEMBLY LANGUAGE PROGRAM. The assembly language program development system includes:

- 1. A multi-phase macro assembler.

- 2. A linking loader.

- 3. A symbolic debugger.

## 3.2.3 TEXT EDITORS.

Two text editor programs are included:

- 1. A character oriented editor.

- 2. A cursor-controlled screen editor.

### 3.2.4 UTILITY AND SUPPORT PROGRAMS.

Utility and support programs are available that include:

- 1. File maintenance programs.

- 2. Dump programs.

- 3. Memory test programs.

- 4. Device test programs.

- 5. Line printer spooler system.

- 6. Dynamic system status monitor programs.

- 7. A system generation procedure that allows custom tailoring of the monitor to individual user requirements.

- 8. Text formatting.

## 3.2.5 ALPHABASIC PROGRAM.

The AlphaBasic programming language processor is a full compiler that is disk oriented and supports:

- 1. Strings.

- 2. Multi-dimensioned arrays.

- 3. Disk I/O file accessing.

- A unique variable mapping system for file manipulation in applications programs and for assembly language subroutine processing.

- 5. Assembly language subroutines.

- 6. Terminal independent cursor control.

The AM-100 utilizes floating point hardware so it typically runs several times faster than other Basic systems. It is precise to eleven decimal digits using a three-word binary. floating-point format which is identical to that used by the WD16 instruction set. 1.84 .10

### 3.2.6 ACCOUNTING PACKAGE.

An accounting package is available under special license that includes:

- 1. General ledger.

- 2. Accounts receivable.

- 3. Accounts payable.

- 4. Order entry-inventory control.

- 5. Payroll.

Each of these is a fully interactive, menu-driven, complete system by itself. However, interface is provided between all five modules to create a totally integrated accounting package.

#### 3.2.7 ALPHALISP.

An Alpha Micro version of the programming language LISP is available. It is designed for users that require a language that is both a formal mathematical language and (with extensions) a convenient programming language.

## 3.2.8 ALPHAPASCAL.

ALPHAPASCAL is a systematic procedure-oriented, structured programming language that is available. Adapted from the UCSD/PASCAL system, ALPHAPASCAL utilizes a dynamic paging system that allows the system to run in a small amount of memory.

# SECTION 4 FUNCTIONAL THEORY OF OPERATION

1.1

### 4.0 INTRODUCTION.

This section describes in detail the functional theory of operation of the AM-100 Central Processor Unit (CPU). The first part of this section provides a general description of the configuration of the CPU and its integration into an S-100 Bus system. The second part describes the details of CPU operation and how the CPU chip set operates with its associated logic elements. The third part provides a complete description of the CPU chip set and the fourth part describes the operation of the individual logic elements that support the CPU chip set.

## 4.1 CPU CONFIGRUATION.

The AM-100 circuit cards function as a 16-bit CPU that plugs in to an S-100 Bus system. The data processing logic is contained on a two-board set that is fully integrated into an S-100 Bus system.

#### 4.1.1 AM-100 TWO-BOARD SET.

The AM-100 CPU is packaged on two circuit boards connected together by a 40-conductor flat ribbon cable. Both boards mate with the standard 100 pin connectors in the S-100 Bus system.

One Circuit board, CPU No. 1, contains the CPU chip set that consists of five 40-pin MOS/LSI chips. This chip set contains the necessary data processing capability for CPU operation. The second circuit board, CPU No. 2, contains the logic that interfaces the 16-bit bus of the CPU to the 8-bit S-100 bus plus the DMA and interrupt logic. The CPU chip set contains six 16-bit accumulators/index registers, a stack pointer and program counter, eight addressing modes, hardware SAVE and RESTORE, and hardware floating point arithmetic.

#### 4.1.2 S-100 BUS OPERATION.

The S-100 Bus system is the single bus computer architecture that supports the AM-100 CPU and its associated memory and peripherals. The I/O connectors are standard 100-pin type and each of the 100 lines are bussed together throughout the computer chassis.

The S-100 bus is an eight-bit format with eight bits of tri-state data for CPU input, eight for CPU output, 16 bits for address, and various control, status, and utility lines. There are also eight lines for vectored interrupts/DMA requests and eight for DMA Grant lines. The various devices connected to the bus are referred to as bus master and bus slave depending on the operational configuration taking place. The CPU is not the only device that can control the bus. Any DMA device has the capability of controlling the bus as a bus master.

The command and control lines determine the timing of the bus and are listed in Table 4-1. The status lines are associated with the address lines and indicate what type of bus cycle is taking place. Any bus master must generate these signals or at least ensure that the unasserted level is maintained. The AM-100 status lines are listed in Table 4-2. The utility lines are clocks, power, and initialization and are listed in Table 4-3.

Table 4-1. S-100 Bus Command/Control Lines

| SIGNAL | NAME                        |

|--------|-----------------------------|

| PSYNC  | Processor Sync              |

| PDBIN  | Data Bus In                 |

| PWR    | Write Strobe                |

| PHLDA  | P-Hold Acknowledge          |

| PHOLD  | Processor Hold Request Line |

Table 4-2. S-100 Bus Status Lines

| SIGNAL                        | NAME                                                            |

|-------------------------------|-----------------------------------------------------------------|

| SM1<br>SOUT<br>SINP           | Bus Master OP Code Fetch<br>I/O Output Cycle<br>I/O Input Cycle |

| SINF<br>SMEMR<br>SWO<br>SINTA | Memory Read Cycle<br>Bus Master Output<br>Interrupt Acknowledge |

Table 4-3. S-100 Bus Utility Lines

| SIGNAL | NAME                       |

|--------|----------------------------|

| Power  | GND, +8VDC, +16VDC, -16VDC |

| Ø2     | 2 MHz Phase 2 Clock        |

| CLOC   | 2 MHz Clock                |

| MWRITE | Memory Write               |

| PRESET | Preset                     |

| POC    | Power-On Clear             |

1 7 L 1 LL.

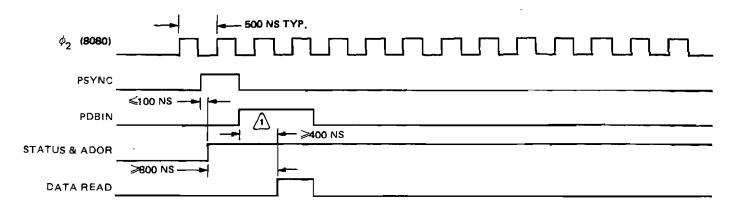

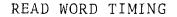

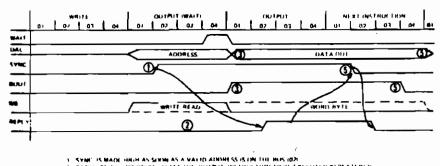

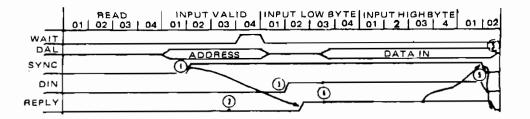

Read Timing. The timing of the signals involved with a READ BYTE sequence on the S-100 bus is shown in Figure 4-1. When an I/O operation takes place, PSYNC is generated as the first state of the bus cycle. Signal PDBIN is next to indicate that a read operation is taking place. Address lines are valid shortly after PSYNC and remain so until the next bus operation. The addressed memory or peripheral has 400ns to place its data on the bus for the read cycle. Once the CPU reads the data, PDBIN is lowered, ending the cycle. The READ WORD cycle is a similar sequence twice because two bytes are read. Timing for the READ WORD sequence is also shown in Figure 4-1.

eranner L

> a a

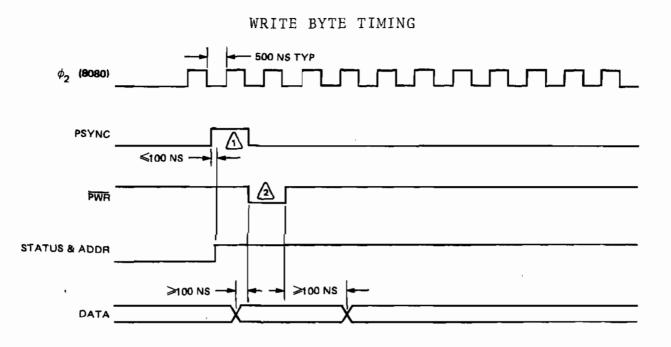

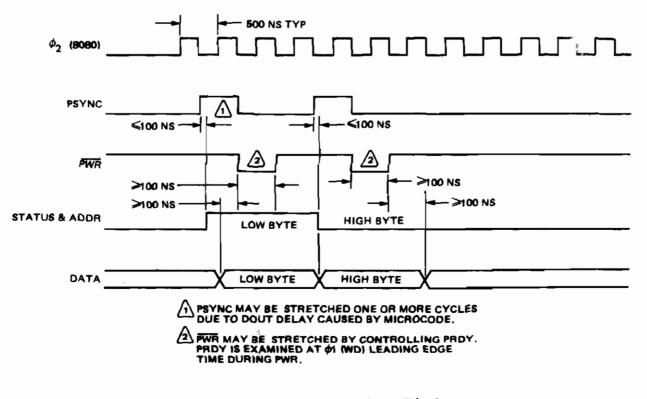

Write Timing. The timing of the signals involved with a WRITE BYTE sequence on the S-100 bus is shown in Figure 4-2. With this sequence, PSYNC starts the bus cycle like the read timing. Signal PWR occurs next to indicate that there is valid data on the bus that is to be written into the addressed location. Status and address data is placed on the bus  $\leq$  100 nsec after PSYNC by the bus master. The WRITE WORD cycle is a similar sequence twice because two bytes are written as shown in Figure 4-2.

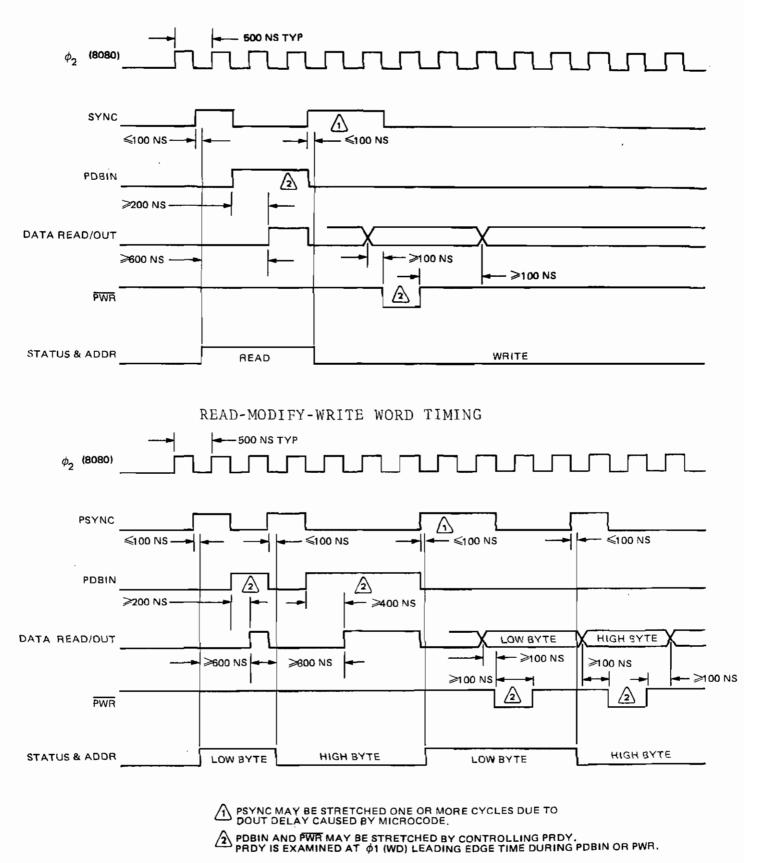

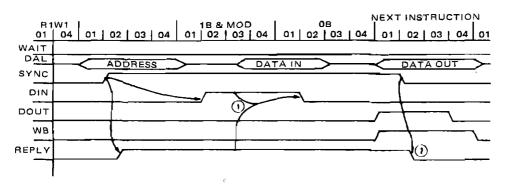

Read-Modify-Write Timing. The READ-MODIFY-WRITE cycle combines these operations into a single sequence as is shown in Figure 4-3.

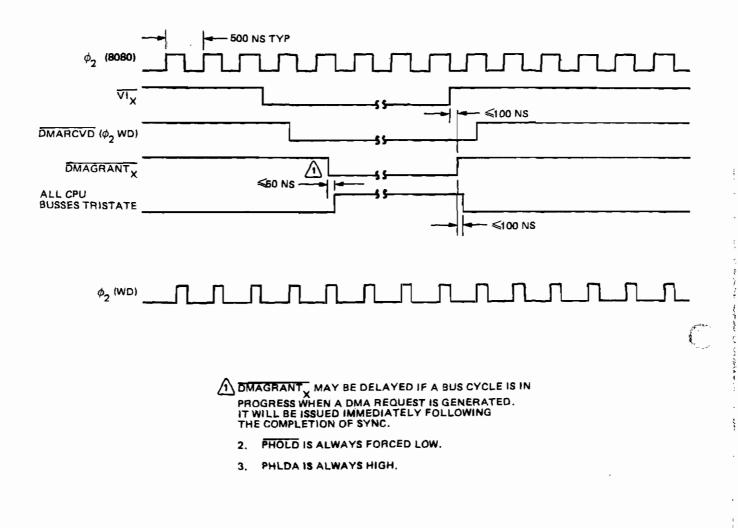

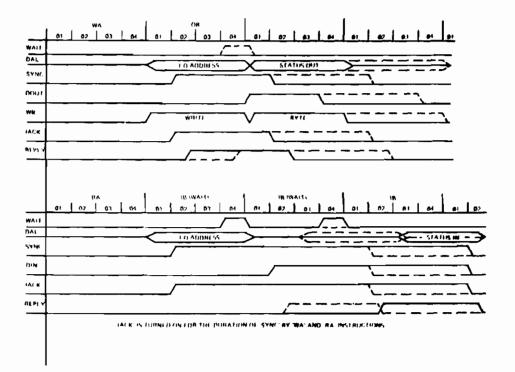

DMA Timing. The timing and sequence for a DMA cycle is shown in Figure 4-4. The selected vector interrupt signal initiates this cycle and it is acknowledged by DMARCVD. The selected DMAGRANT signal indicates an active DMA cycle and the busses are active < 50ns later.

#### READ BYTE TIMING

٩

-

WRITE WORD TIMING

Į

Figure 4-2. S-100 Write Timing

Figure 4-3. S-100 Bus Read-Modify-Write Timing

.....

DMA TIMING

()

Figure 4-4. S-100 Bus DMA Timing

For a complete description of the S-100 bus signals in the AM-100 system, refer to Table 4-4. This table lists all signals in alphabetical order with AM-100 pin numbers and also the sheet number of the schematic where they interface with the AM-100 CPU. A complete description of each signal is also given.

۲

| SIGNAL | NAME        | J1<br>PIN NO. | SCHEM<br>PAGE   | DESCRIPTION                                    |

|--------|-------------|---------------|-----------------|------------------------------------------------|

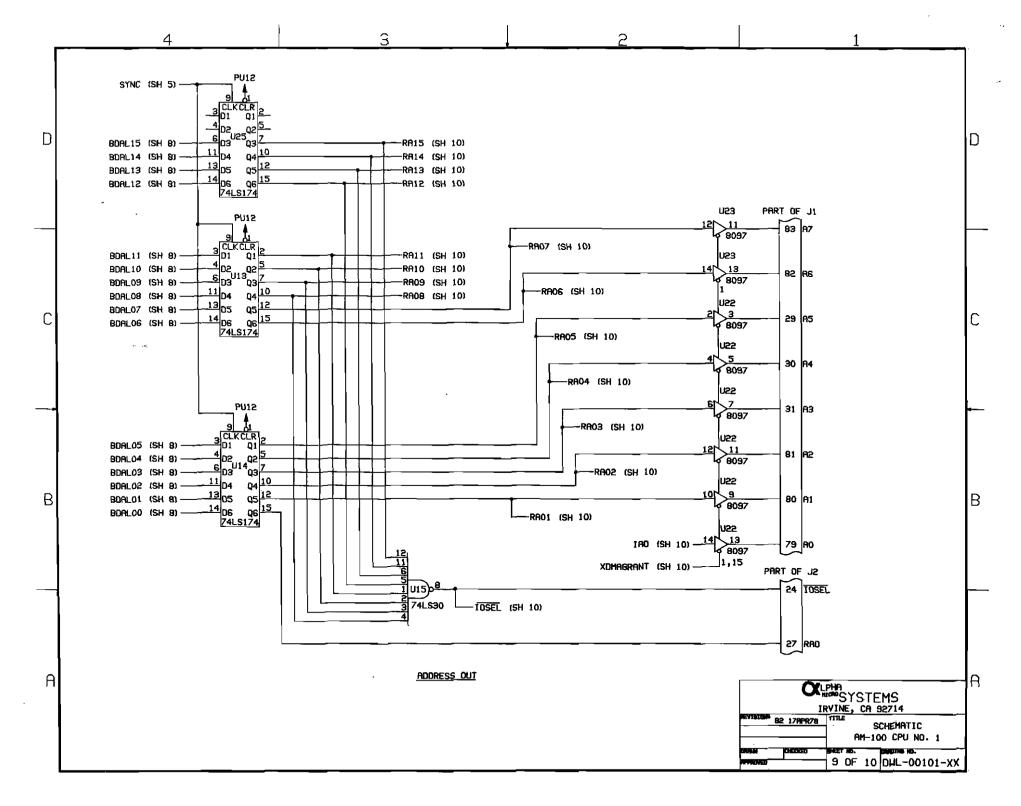

| A0     | Address 0   | 79            | CPU1-9          | 16 bits of tri-state addressing.               |

| A1     | Address 1   | 80            | CPU1-9          |                                                |

| A2     | Address 2 · | 81            | CPU1-9          |                                                |

| A3     | Address 3   | 31            | CPU1-9          |                                                |

| A4     | Address 4   | 30            | CPU1-9          |                                                |

| A5     | Address 5   | 29            | CPU1-9          |                                                |

| A6     | Address 6   | 82            | CPU1-9          |                                                |

| A7     | Address 7   | 83            | CPU1 <b>-</b> 9 |                                                |

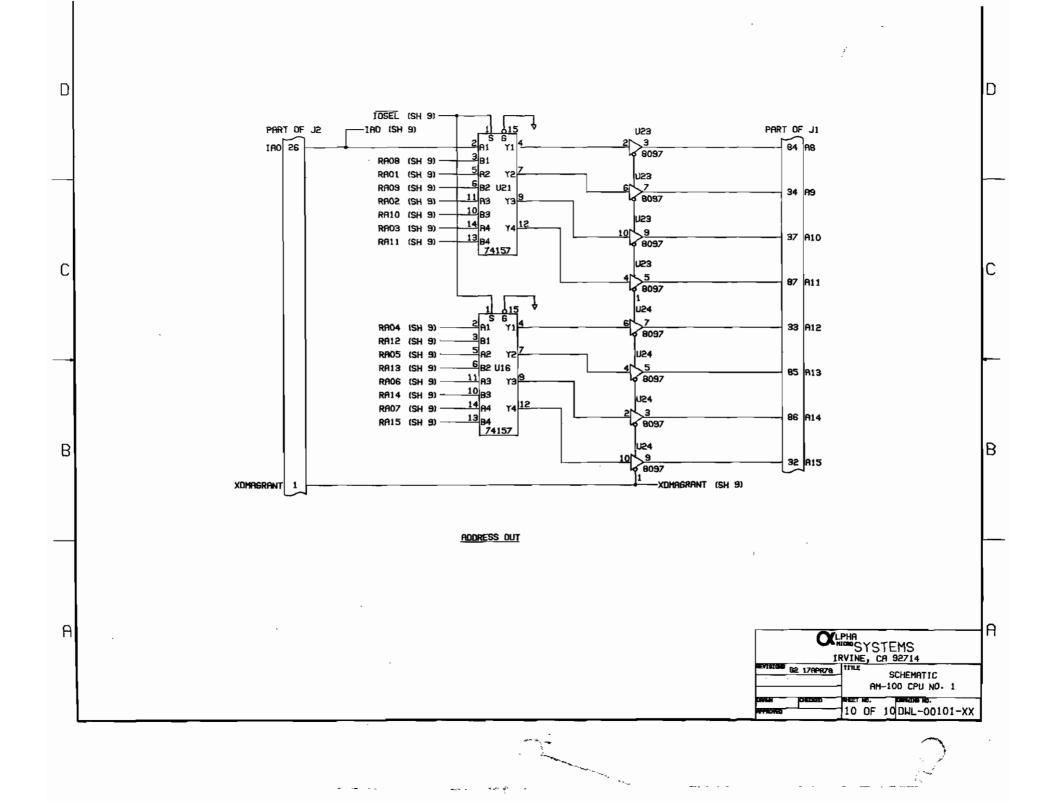

| A 8    | Address 8   | 84            | CPU1-10         |                                                |

| A9     | Address 9   | 34            | CPU1-10         |                                                |

| A10    | Address 10  | 37            | CPU1-10         |                                                |

| A11    | Address 11  | 87            | CPU1-10         |                                                |

| A12    | Address 12  | 33            | CPU1-10         |                                                |

| A13    | Address 13  | 85            | CPU1-10         |                                                |

| A14    | Address 14  | 86            | CPU1-10         |                                                |

| A15    | Address 15  | 32            | CPU1-10         |                                                |

| CLOC   | 2 MHz Clock | 49            | CPU2-3          | 2 MHz clock from same source as $\emptyset$ 2. |

Table 4-4. S-100 Bus Interface Signals List

•

$\sum$

| SIGNAL | NAME               | J1<br>PIN NO. | SCHEM<br>PAGE | DESCRIPTION                                                                                                                                                 |

|--------|--------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

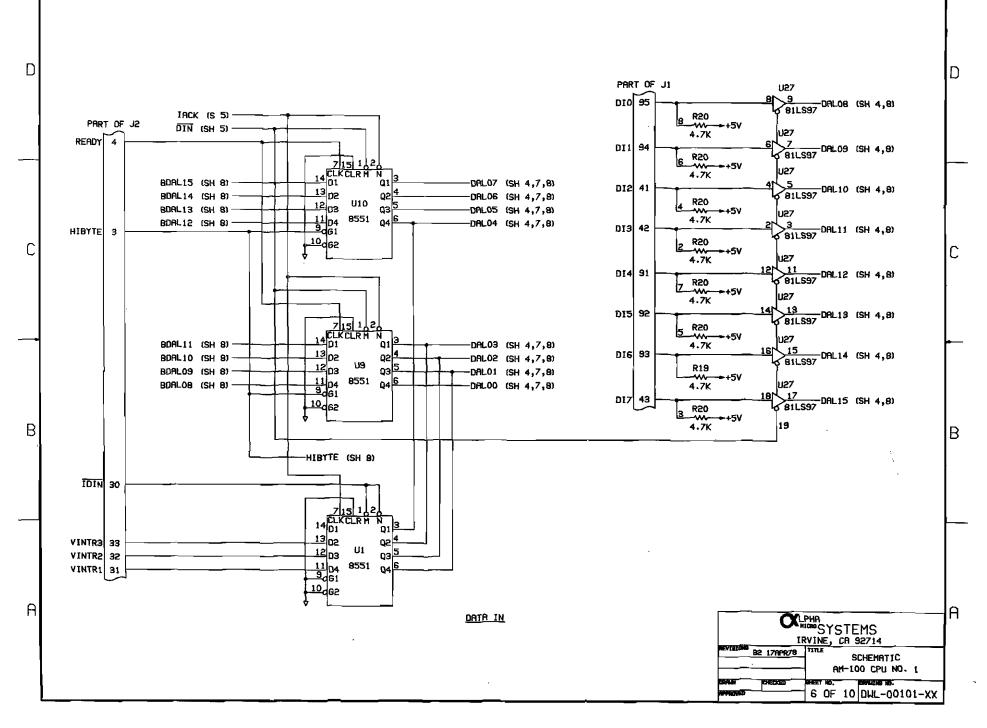

| DIO    | Data Input Bus     | 95            | CPU1-6        | Data input port. Eight bit tri-state data bus                                                                                                               |

| DI1    | Bits 0-7.          | 94            | CPU1-6        | from bus slave to bus master.                                                                                                                               |

| DI2    |                    | 41            | CPU1-6        |                                                                                                                                                             |

| DI3    |                    | 42            | CPU1-6        |                                                                                                                                                             |

| DI4    | · reticue :        | 91            | CPU1-6        |                                                                                                                                                             |

| DI5    | • <b>14</b> 2.2 m. | 92            | CPU1-6        |                                                                                                                                                             |

| DI6    |                    | 93            | CPU1-6        |                                                                                                                                                             |

| D17    |                    | 43            | CPU1-6        |                                                                                                                                                             |

| DMAGRO | DMA Grant          | 63            | CPU2 - 5      | Grant signal issued to the highest priority                                                                                                                 |

| DMAGRI |                    | 62            | CPU2 - 5      | controller that has requested the bus.                                                                                                                      |

| DMAGR2 |                    | 61            | CPU2 - 5      |                                                                                                                                                             |

| DMAGR3 |                    | 60            | CPU2-5        |                                                                                                                                                             |

| DMAGR4 |                    | 59            | CPU2 - 5      |                                                                                                                                                             |

| DMAGR5 |                    | 58            | CPU2-5        |                                                                                                                                                             |

| DMAGR6 |                    | 57            | CPU2-5        |                                                                                                                                                             |

| DMAGR7 |                    | 56            | CPU2-5        |                                                                                                                                                             |

| DMARCV | D DMA Received     | 64            | CPU2-5        | CPU response to DMA request indicating that a DMA<br>exchange is in process. No other DMA controllers<br>may issue a DMA request while DMARCVD is asserted. |

Table 4-4 (Cont.). S-100 Bus Interface Signals List

4-11

2 ×

| SIGNAL                                               | NAME                     | J1<br>PIN NO.                                | SCHEM<br>PAGE                                                                          | DESCRIPTION                                                                                                                                                                   |

|------------------------------------------------------|--------------------------|----------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

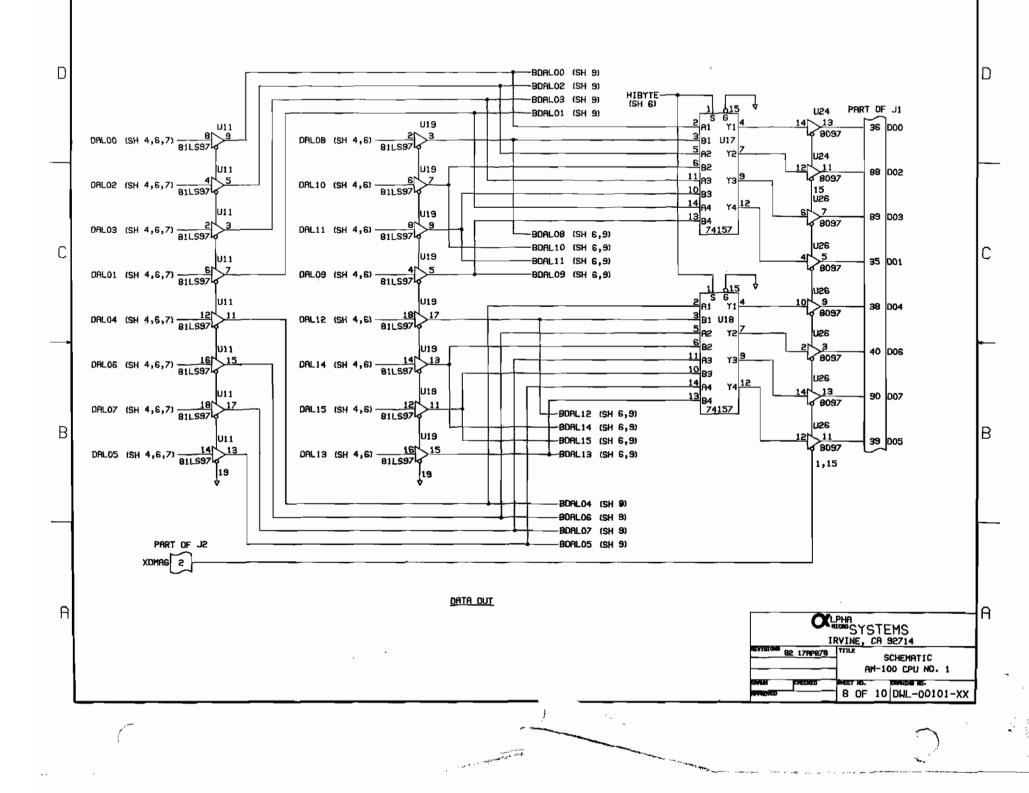

| D00<br>D01<br>D02<br>D03<br>D04<br>D05<br>D06<br>D07 | Data Out Bus<br>Bits 0-7 | 36<br>35<br>88<br>89<br>38<br>39<br>40<br>90 | CPU1-8<br>CPU1-8<br>CPU1-8<br>CPU1-8<br>CPU1-3<br>CPU1-8<br>CPU1-8<br>CPU1-8<br>CPU1-8 | Data output port. Eight bit tri-state data bus<br>from bus master to bus slave.                                                                                               |

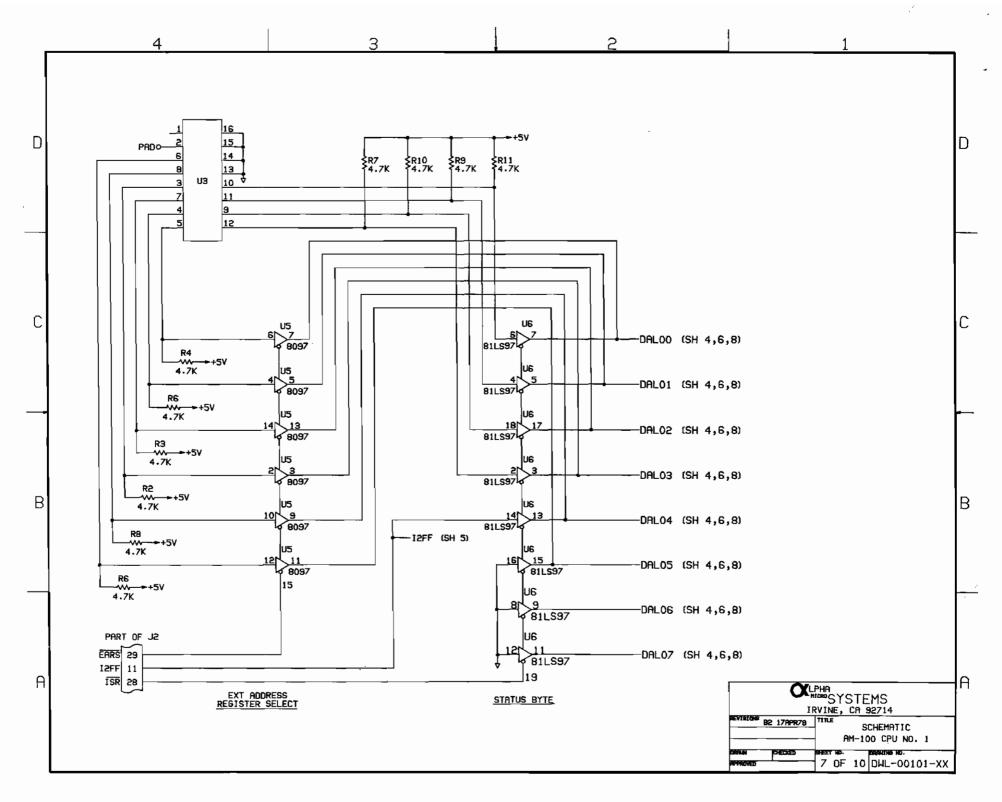

| ENDF                                                 |                          | 18<br>19<br>22                               | CPU2-2                                                                                 | Only used internal to the AM-100                                                                                                                                              |

| MWRITE                                               | Memory Write             | 68                                           | CPU2 - 2                                                                               | Gated combination of PWR and SOUT.                                                                                                                                            |

| PDBIN                                                | Data Bus In              | 78                                           | CPU2-9                                                                                 | Read Enable. Used by bus master to request address slave to place data on the data bus.                                                                                       |

| PHLDA                                                | P-Hold                   | 26                                           | CPU2 - 3                                                                               | When asserted, indicates that the CPU is<br>releasing control of the bus in response to a<br>DMA request (PHOLD). (This signal is forced<br>high by the AM-100 and not used.) |

Table 4-4 (Cont.). S-100 Bus Interface Signals List

# Table 4-4 (Cont.). S-100 Bus Interface Signals List

| SIGNAL | NAME                     | J1<br>PIN NO. | SCHEM<br>PAGE | DESCRIPTION                                                                                                       |

|--------|--------------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------------------|

| PHOLD  | DMA Request              | 74            | CPU2 - 2      | Used by DMA controllers to request bus master-<br>ship. (This signal is held low by the AM-100<br>and not used.)  |

| PINTE  | CPU Interrupt<br>"Enable | 28            | CPU2 - 7      | Output from CPU to enable slave interrupts (not used by Alpha Micro Systems).                                     |

| POC    | Power On Clear           | 99            | CPU2-3        | Clear signal generated by the CPU on initial turn on.                                                             |

| PRESET | Preset                   | 75            | CPU2-2        | Reset signal normally originating from front<br>panel reset pushbutton.                                           |

| PSYNC  | Processor Sync           | 76            | CPU2-7        | When asserted, indicates the start of a bus cycle.                                                                |

| PWAIT  | CPU Wait                 | 27            | CPU2 - 7      | When asserted, indicates that the CPU is in a wait period.                                                        |

| PWR    | Write Strobe             | 77            | CPU2 - 7      | When asserted, is a command from the bus master<br>for the addressed slave to accept the data on<br>the data bus. |

| SIGNAL | NAME                        | J1<br>PIN NO. | SCHEM<br>PAGE | DESCRIPTION                                                                                      |

|--------|-----------------------------|---------------|---------------|--------------------------------------------------------------------------------------------------|

| SINP   | I/O Input Cycle             | 46            | CPU2 - 7      | When asserted, indicates that the current bus cycle is a bus master input from an I/O address.   |

| SINTA  | Interrupt<br>Acknowledge    | 96            | CPU2 - 7      | When asserted, indicates acceptance by bus master of an interrupt request.                       |

| SMEMR  | Memory Read Cycle           | 47            | CPU2 - 7      | When asserted, indicates that the current bus cycle is a bus master input from a memory address. |

| SM1    | Bus Master<br>OP Code Fetch | 44            | CPU2 - 7      | When asserted, indicates that the current bus cycle is a bus master OP code fetch.               |

| SOUT   | I/O Output Cycle            | 45            | CPU2-7        | When asserted, indicates that the current bus cycle is a bus master output to an I/O address.    |

| SWO    | Bus Master<br>Output        | 97            | CPU2 - 7      | When asserted, indicates that the current bus cycle is a bus master output.                      |

-

# Table 4-4 (Cont.). S-100 Bus Interface Signals List

4-14

۲

| SIGNAL                                                                                  | NAME                                                                                                                                                                                                                 | J1<br>PIN NO.                          | SCHEM<br>PAGE                                                                                            | DESCRIPTION                                                                    |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| VI0         VI1         VI2         VI3         VI4         VI5         VI6         VI7 | Vectored Interrupt 0<br>Vectored Interrupt 1<br>Vectored Interrupt 2<br>Vectored Interrupt 3<br>Vectored Interrupt 4<br>Vectored Interrupt 5<br>Vectored Interrupt 5<br>Vectored Interrupt 6<br>Vectored Interrupt 7 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | CPU2 - 5<br>CPU2 - 6 | Vectored interrupt lines used for both<br>interrupt requests and DMA requests. |

| STVAL                                                                                   | Status Valid                                                                                                                                                                                                         | 25                                     | CPU2-3                                                                                                   | Indicates Status & Address lines valid<br>during PSYNC.                        |

| Ø2                                                                                      | Phase 2 Clock                                                                                                                                                                                                        | 24                                     | CPU2 - 3                                                                                                 | 2 MHz clock Phase 2. Master Timing signal for the bus.                         |

| +8V                                                                                     | +8vdc power                                                                                                                                                                                                          | 1, 51<br>1, 51                         | CPU1-1<br>CPU2-1                                                                                         | System power and ground.                                                       |

| +16V                                                                                    | +16 vdc power                                                                                                                                                                                                        | 2                                      | CPU1-1                                                                                                   |                                                                                |

| -16V                                                                                    | -16 vdc power                                                                                                                                                                                                        | 52                                     | CPU1-1                                                                                                   |                                                                                |

| GND                                                                                     | Gnd                                                                                                                                                                                                                  | 50,                                    | CPU1-1                                                                                                   |                                                                                |

|                                                                                         |                                                                                                                                                                                                                      | 100                                    | CPU2-1                                                                                                   |                                                                                |

•

.....

· · · ·

Table 4-4 (Cont.). S-100 Bus Interface Signals List

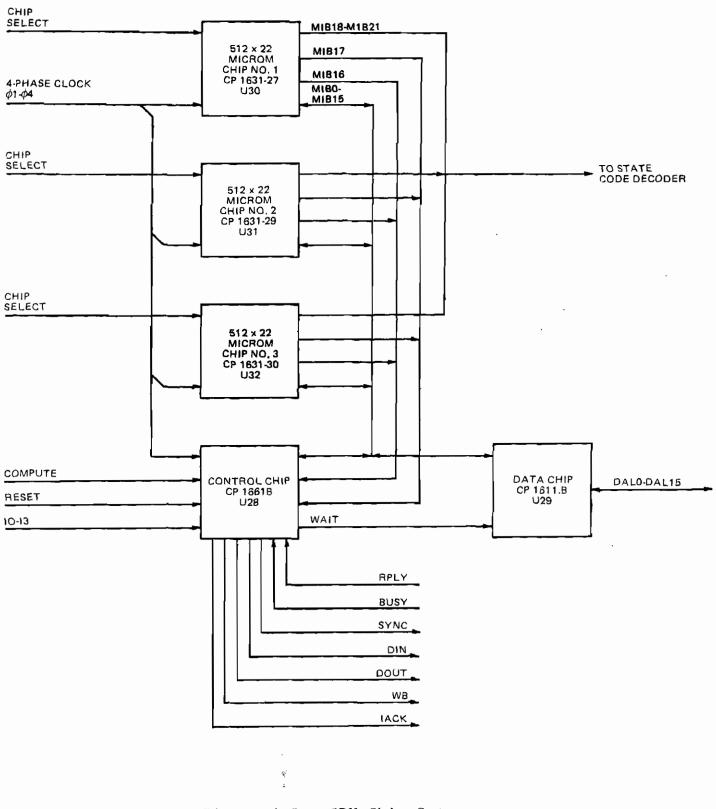

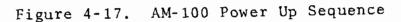

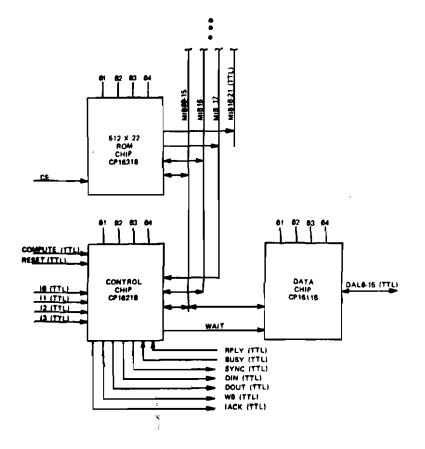

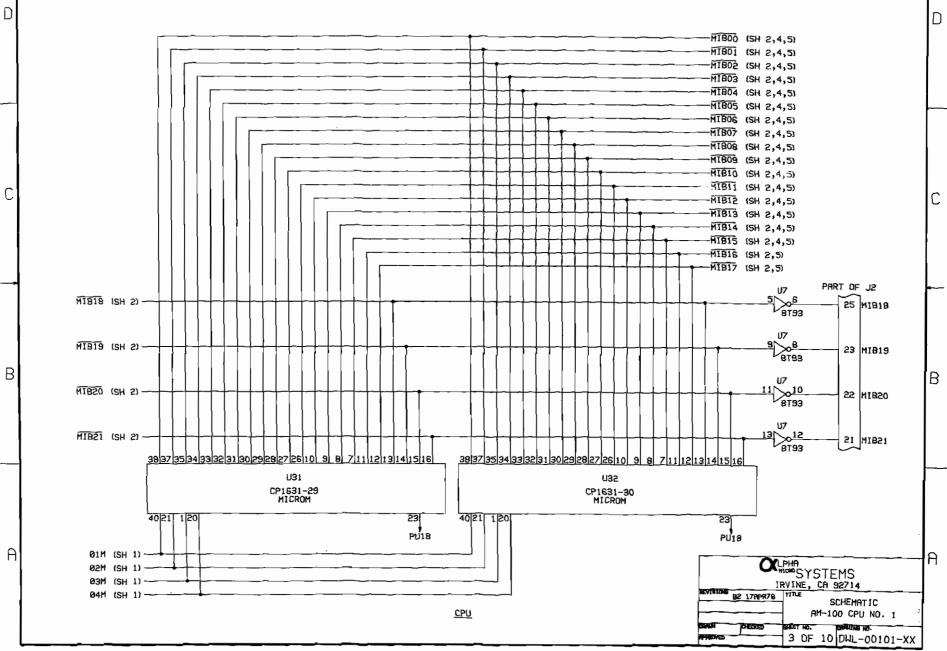

4.1.3 CPU CHIP SET.

The CPU chip set consists of five 40-pin MOS/LSI chips that include a data chip, a control chip, and three microms. A detailed description of the operation of the individual chips is contained in paragraph 4.3. The chip set utilizes 16-bit architecture with both word and byte operation. Since the S-100 Bus is an eight-bit system, further data processing is required for compatibility and this is described in paragraph 4.2. The primary features of the chip are as follows:

- a. 16-bit architecture with both word and byte operation.

- b. 16-bit data access port to memory and I/O.

- c. Eight 16-bit registers.

- d. Four external interrupts.

- e. Three internal interrupts.

- f. Eight addressing modes.

The chip set is microprogrammable by the coded data within the microms. Figure 4-5 contains a block diagram of the five chips in the CPU chip set.

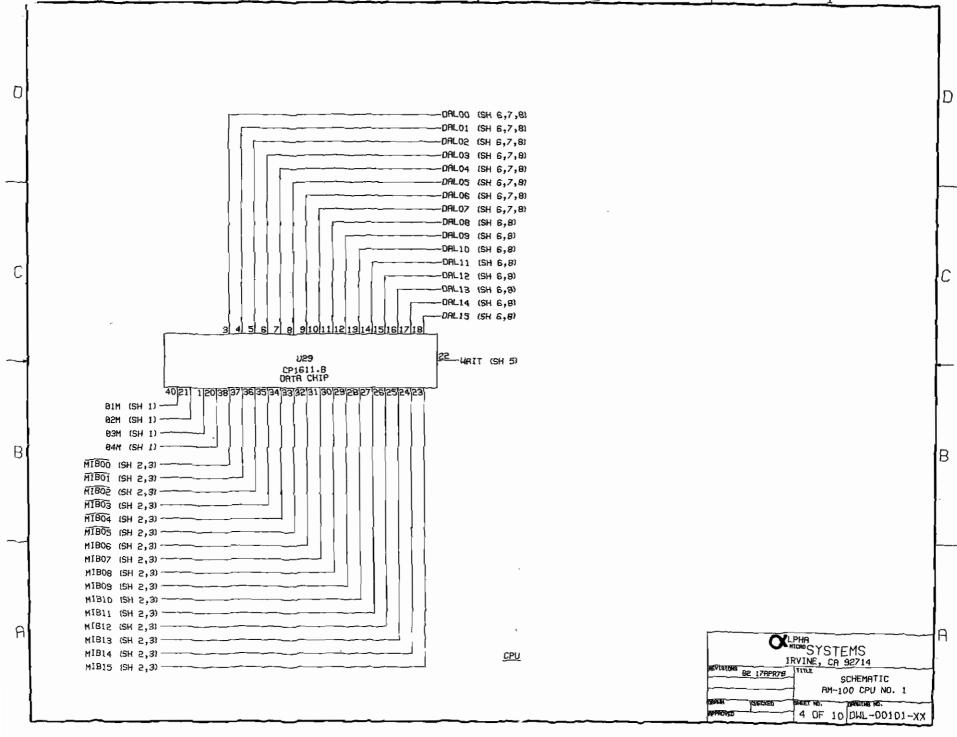

#### 4.1.3.1 DATA CHIP.

The data chip provides the interfacing capability for data and addressing. A 16-bit Data and Address bus (DAL) interfaces the CPU to external logic. It also contains eight 16-bit registers, the Arithmetic Logic Unit (ALU), microinstruction bus lines, and some microinstruction decoding logic.

Figure 4-5. CPU Chip Set

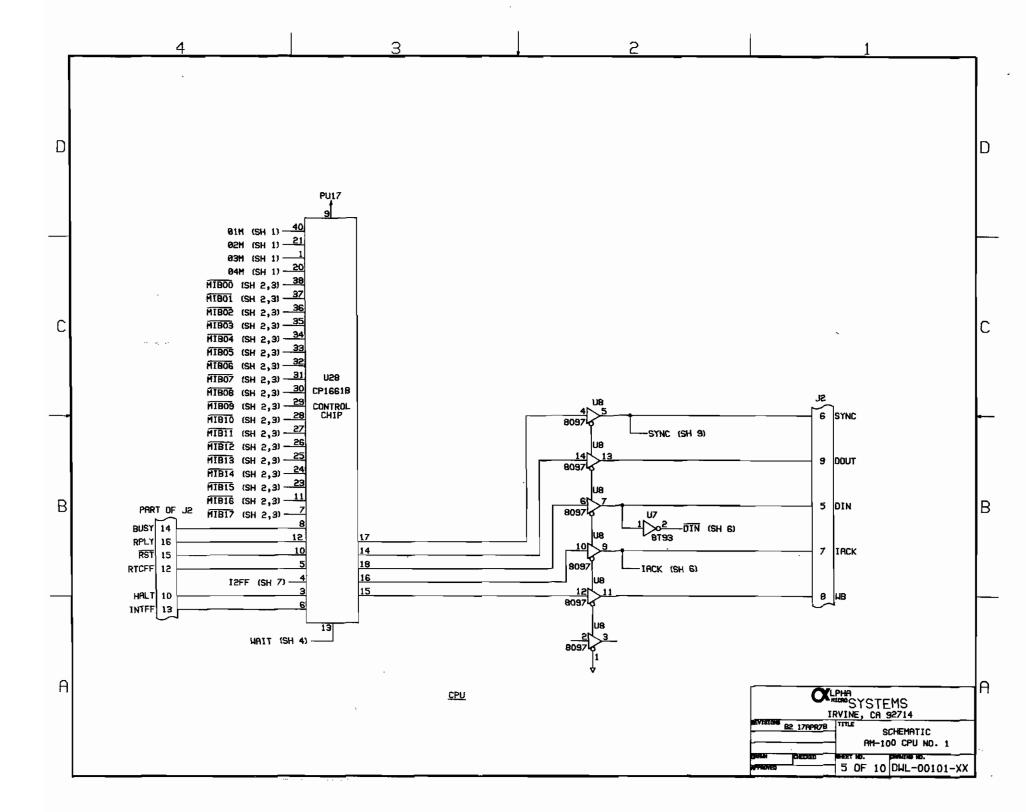

## 4.1.3.2 CONTROL CHIP.

The control chip contains the microinstruction address register which controls accessing of the microinstructions. It also contains translation array logic and the interrupt logic. The master timing control is directed by the control chip which indicates when an address is valid on the DAL lines and indicates a read or write operation and a byte or word operation.

$\gamma = e_{1}^{2} + e_{2}^{2}$

#### 4.1.3.3 MICROM CHIPS.

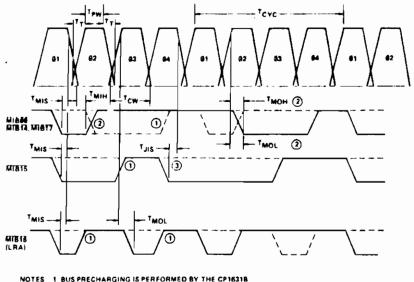

The microm chips are 512 word by 22 bit ROMs which are programmed to Alpha Micro specifications. These 22-bit outputs comprise the microinstruction bus (MIB) that allows the chips in the CPU to communicate with each other (MIB00-MIB21). Each ROM location contains a 16-bit microinstruction, two control bits, and four auxiliary bits. The 16-bit microinstructions and the two control bits form a high impedance tri-state bus. Bits MIB18-MIB21 are the auxiliary bits and are the state codes that direct external logic to perform special functions.

#### 4.1.3.4 MICROINSTRUCTION BUS.

The Microinstruction Bus (MIB) is a high impedance MOS bus for data transmission between the chips in the CPU and is very sensitive to external monitoring even with oscilloscope probes. The capacitors located on CPU 1 suppress noise and optimize data transmission on the bus.

Bits MIB00-MIB10 serve a dual purpose. During the portion of the cycle that addresses the microinstruction from the microm, these bits contain the 11-bit address. During another part of the cycle, they are used to transmit the microinstruction to the other chips. Bits MIB11-MIB17 just transfer part of the microinstruction. Therefore, during the address phase, MIB00-MIB10 address the microinstruction and during another phase MIB00-MIB17 transfer the microinstruction.

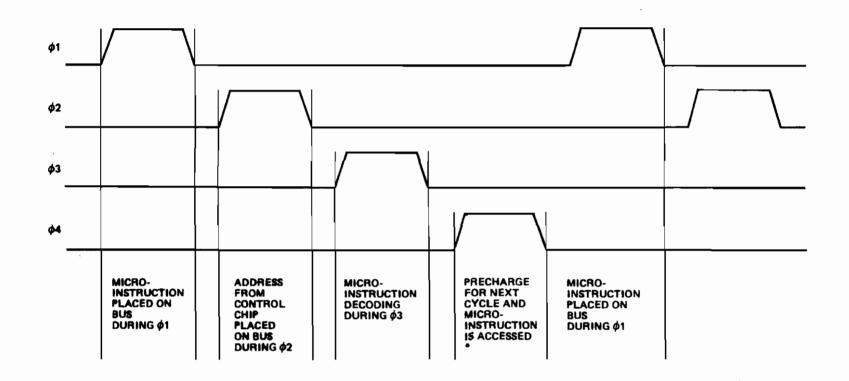

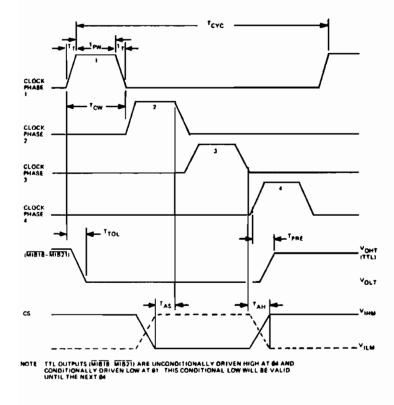

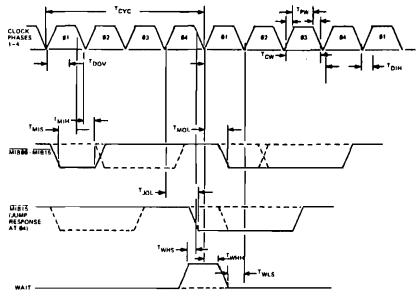

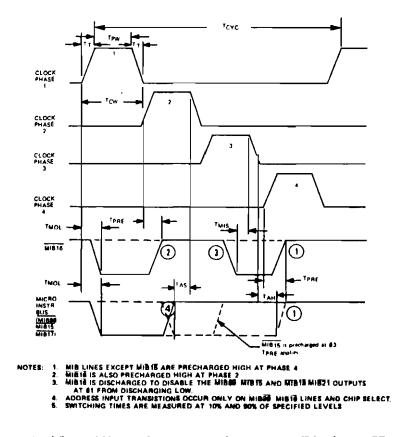

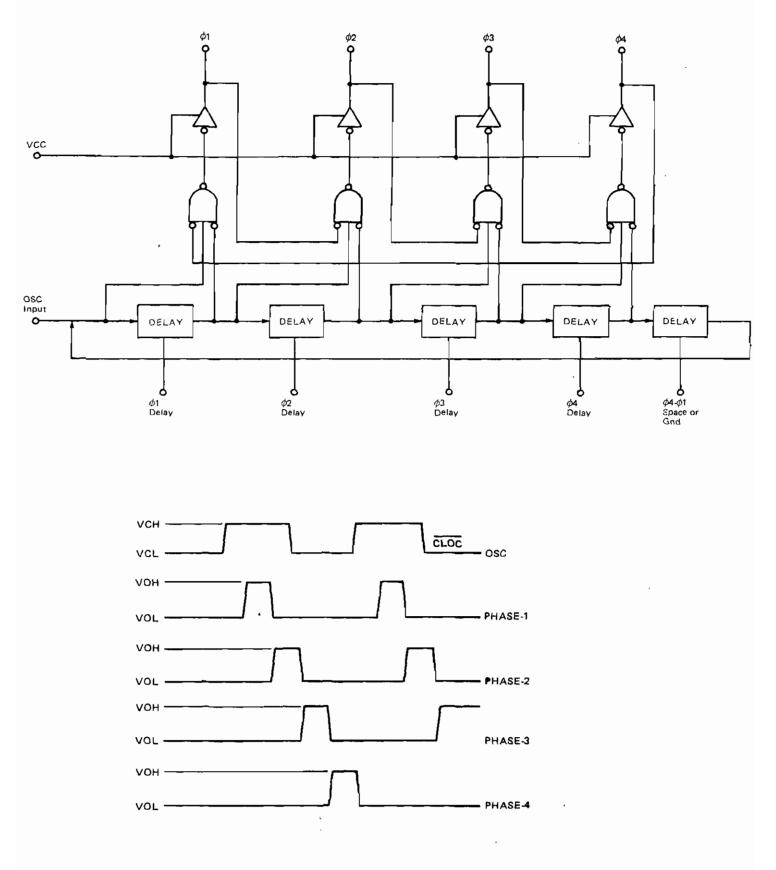

Timing of the microinstruction bus is shown in Figure 4-6. The four phases are running continuously, and phase two places the address of the next required microinstruction on the MIB in bits 0-10. This address data comes from the control chip. Phase three decodes the microinstruction. Phase four provides the precharge necessary for the nodes since this is a MOS bus. At phase 1, the microinstruction is placed on the bus and the process repeats.

The function of the state codes and operation of the CPU with its associated external logic is described in paragraph 4.2.

\*Except for MIB15 which is precharged at  $\emptyset$ 3. It is used to transfer conditional jump results back to the control chip during  $\emptyset$ 4.

MIB16 is precharged during  $\beta 2$  and  $\beta 4$ . It is conditionally discharged during  $\beta 1$  to control RR register, and conditionally discharged during  $\beta 3$  to disable microm output buffers.

Figure 4-6. Microinstruction Bus Timing

#### 4.2 CPU OPERATIONS.

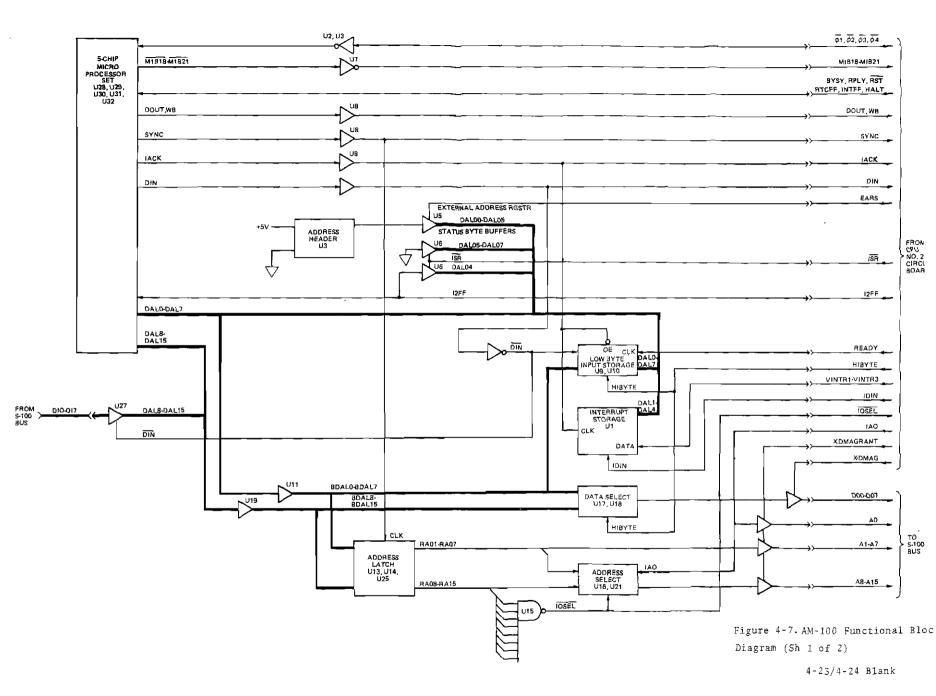

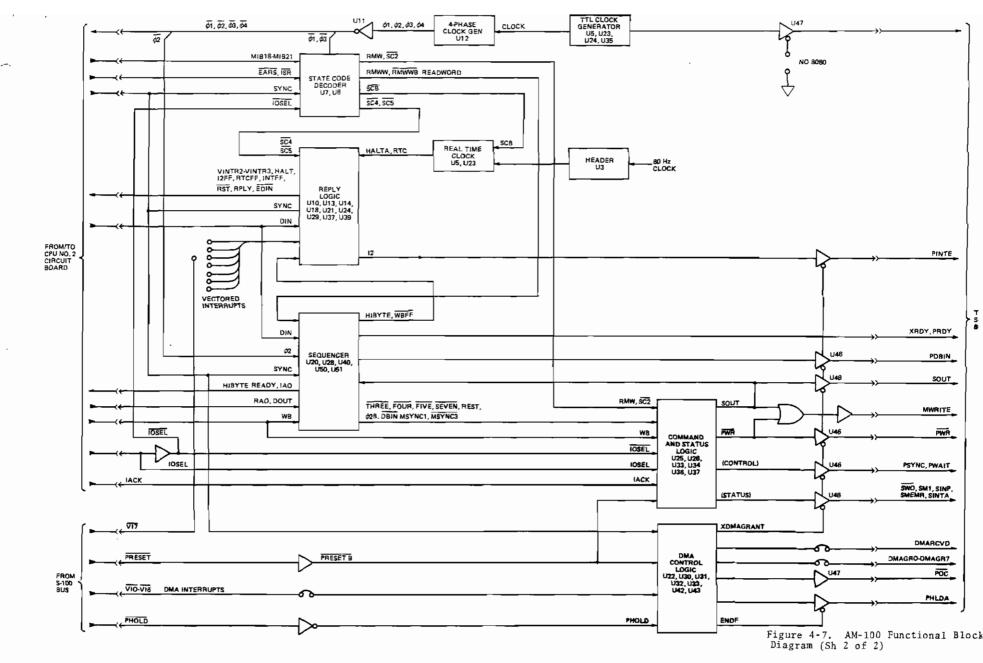

The AM-100 CPU board set consists of the CPU chip set and associated logic elements that provide data processing capability for the S-100 bus system. This Section describes operation of the CPU in the system and operation of the CPU chip set with its associated logic elements.

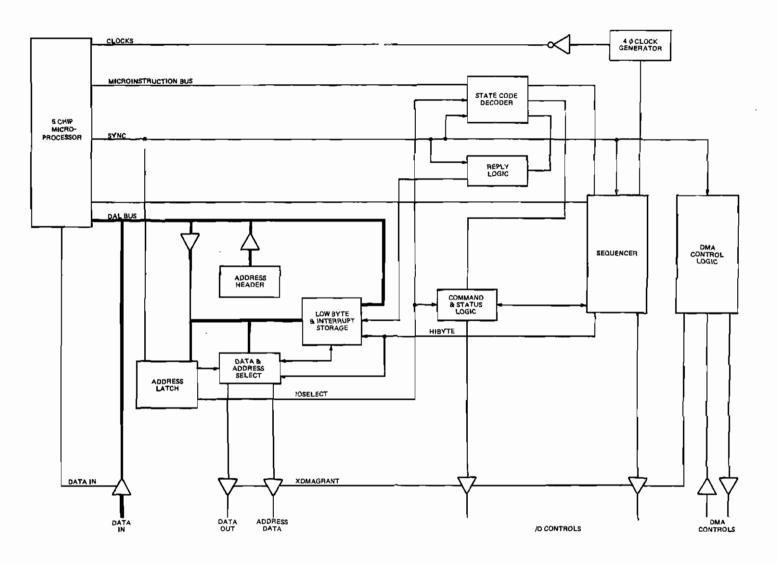

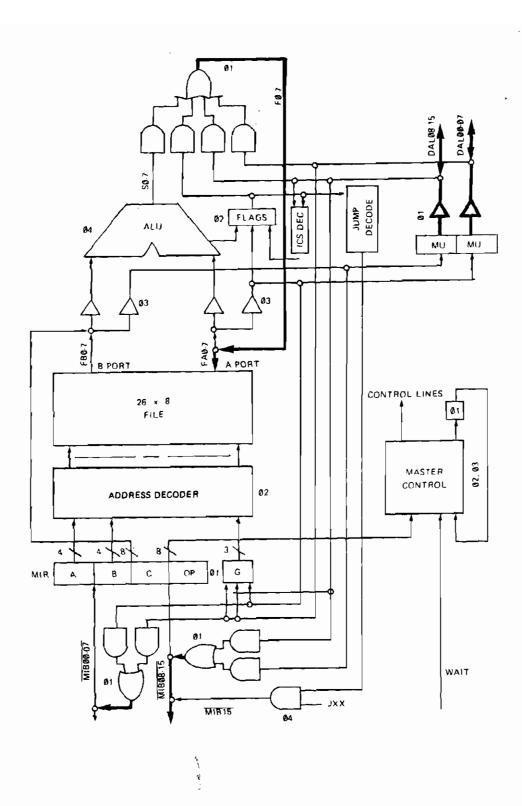

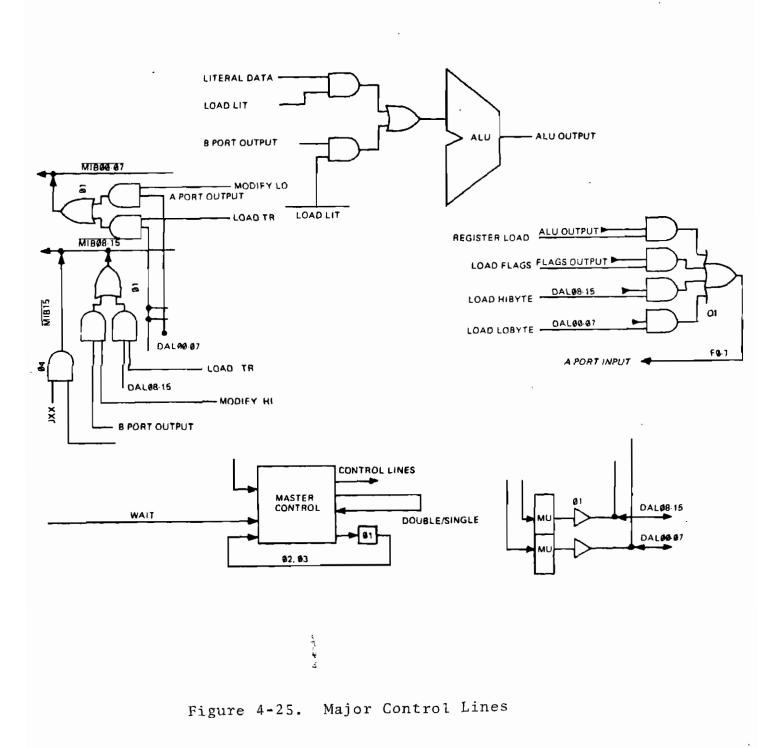

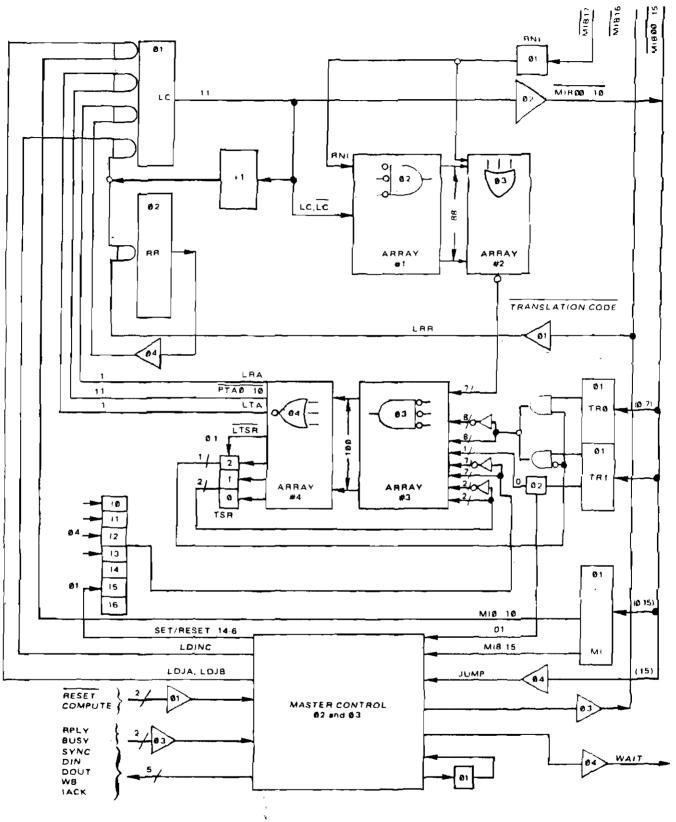

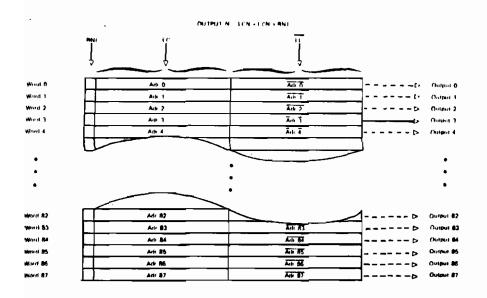

An overall block diagram of the CPU board set is shown in Figure 4-7. Sheet 1 contains all the logic on CPU board 1, and sheet 2 contains all the logic on board 2. Table 4-5 contains a complete list of the signals in the AM-100 CPU. The list is alphabetical by signal mnemonic, and a description is given for the function of each signal and the location where it can be found on the schematic diagram. · · ·

۰. ۲. ۲.

•

4-75/4-76 Rlank

Table 4-1. AM-100 Signals List

~

.

\_

-

.

| SIGNAL            | NAME                                | BOARD<br>NO. | J2<br>PIN NO. | SCHEM PAGE<br>OF SOURCE | FUNCTION                                                                                                                                   |

|-------------------|-------------------------------------|--------------|---------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| BDAL00-<br>BDAL15 | Buffered Data and<br>Address Lines  | 1            | -             | CPU1-8                  | Internal tri-state bus for Data and Address Lines.                                                                                         |

| BUSY              | Busy                                | 1<br>2       | . 14          | CPU1-5<br>CPU2-5        | Asserted when any of the seven vectored interrupts<br>(VIO-VI6, PHOLD) are received. Indicates that a<br>DMA exchange is in process.       |

| CLOC              | 2 MHz Clock                         | 2            | -             | CPU2-3                  | Output of 2 MHz clock.                                                                                                                     |

| DALOO-<br>DAL15   | Data and Address Lines              | 1            | -             | CPU1-4,<br>6, 7         | Tri-state bus for Data and Address Lines.                                                                                                  |

| DBIN<br>DBIN      | Data Bus In                         | 2            | -             | CPU2-8                  | Read Enable equivalent to PDBIN on S-100 Bus.<br>Enables CPU to read data from the Data In Bus.                                            |

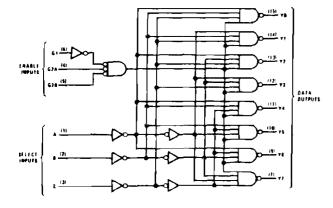

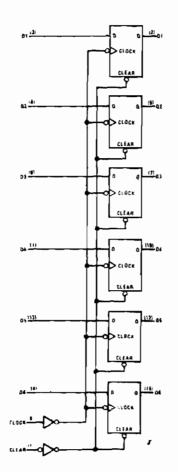

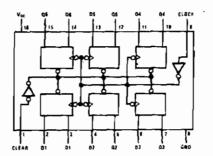

| DIN<br>DIN        | Data In                             | 1<br>2       | 5             | CPU1-5<br>CPU2-6        | Control signal from the processor to cause the<br>address unit to gate its read data on the data lines.                                    |