\*

ŗ

|                                                                                                                  | <u>6</u> ; | 3 - 1 - 2 |

|------------------------------------------------------------------------------------------------------------------|------------|-----------|

|                                                                                                                  |            |           |

| and the second |            |           |

| and the second |            |           |

| TABLE OF CONTENTS                                                                                                |            |           |

|                                                                                                                  | Page       |           |

## Paragraph

•

. .

,

•

.

Page

|         | SECTION 1 GENERAL DESCRIPTION                |

|---------|----------------------------------------------|

| 1.0     | Introduction 1-1                             |

| 1.1     | Circuit Board Description 1-1                |

| 1.2     | Application 1-1                              |

|         |                                              |

|         | SECTION 2 OPERATING DATA                     |

| 2.0     | Introduction                                 |

| 2.1     | Capabilities and Specifications 2-1          |

| 2.2     | Interface Description and Wiring 2-3         |

| 2.2.1   | S-100 Bus Interface                          |

| 2.2.2   | Floppy Drive Interface                       |

| 2.2.3   | Wiring and Connections                       |

| 2.2.3.1 | AM-200 with PERSCI Drive                     |

| 2.2.3.2 | AM-200 with Wangco/Orbis Drive 2-15          |

| 2.3     | User Options                                 |

| 2.3.1   | Address Code                                 |

| 2.3.2   | Interrupt Lines                              |

| 2.3.3   | DMA Request Lines                            |

| 2.3.4   | DMA Received                                 |

| 2.3.5   | DMA Grant Lines                              |

| 2.3.6   | Phantom Feature                              |

| 2.3.6.1 | Application                                  |

| 2.3.6.2 | Modification Procedure for Boards of Rev.B02 |

| 4.5.0.4 | and Above                                    |

| 2767    |                                              |

| 2.3.6.3 | Modification Procedure for Boards Below Rev. |

| 0 7 7   | B02                                          |

| 2.3.7   | 8080 and CPM System Modification 2-21        |

| 2.3.7.1 | Application                                  |

| 2.3.7.2 | Modification Procedure                       |

**K**:-

é

| Paragraph |                                          | Page      |

|-----------|------------------------------------------|-----------|

| •         | SECTION 3 PROGRAMMING                    |           |

| 3.0       | Introduction                             | . 3-1     |

| 3.1       | Addressing                               | . 3-1     |

| 3.2       | External Control Register                | . 3-1     |

| 3.3       | Bootstrap Loader                         | . 3-4     |

|           |                                          |           |

|           | SECTION 4 FUNCTIONAL THEORY OF OPERATION |           |

| 4.0       | Introduction                             | . 4-1     |

| 4.1       | Circuit Board Operation                  | . 4-1     |

| 4.1.1     | Addressing                               | . 4-9     |

| 4.1.2     | Bootstrap Prom                           | . 4-9     |

| 4.1.3     | External Control Register                | . 4-10    |

| 4.1.4     | Subsector Register Logic                 | . 4-10    |

| 4.1.5     | DMA Address and Control                  | . 4-11    |

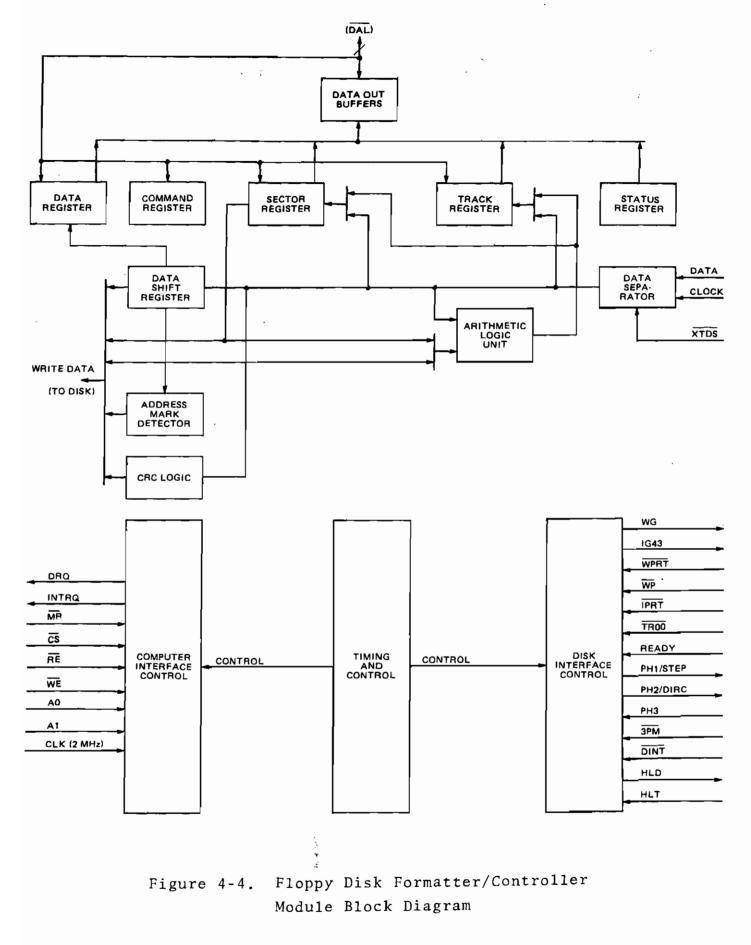

| 4.1.6     | Floppy Disk Formatter/Controller         | . 4-11    |

| 4.1.7     | Disk Read and Write Sequence             | . 4-12    |

| 4.2       | Circuit Module Description               | . 4-14    |

| 4.2.1     | Floppy Disk Formatter/Controller         |           |

|           | Description (U12)                        | . 4-14    |

| 4.2.1.1   | Organization                             | 4 - 20    |

| 4.2.1.2   | Processor Interface :                    | . 4 - 2 3 |

| 4.2.1.3   | Floppy Disk Interface                    | 4-24      |

| 4.2.1.4   | Command Description                      | . 4 - 28  |

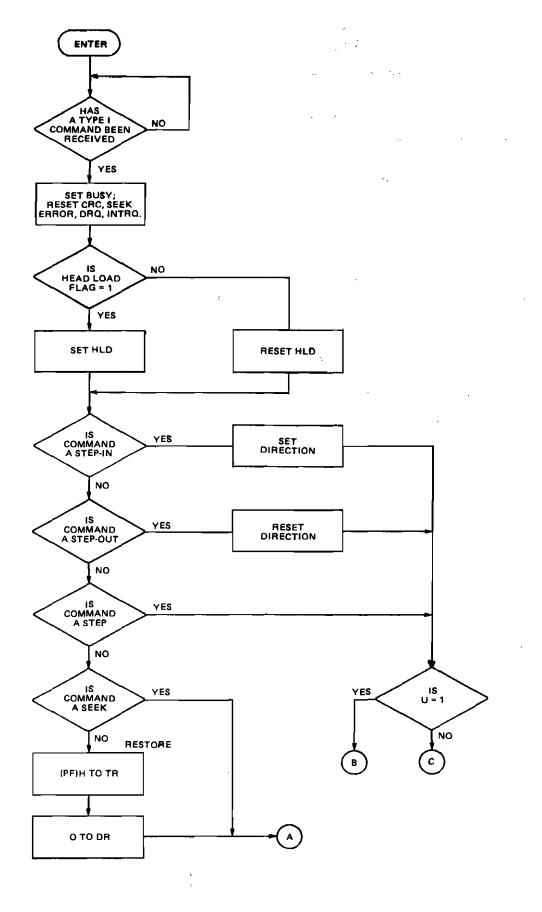

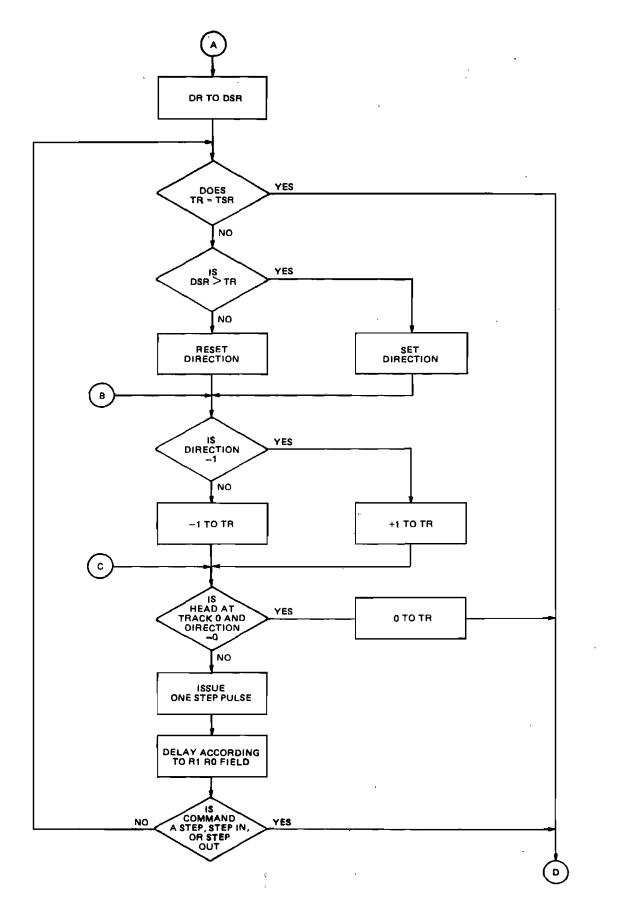

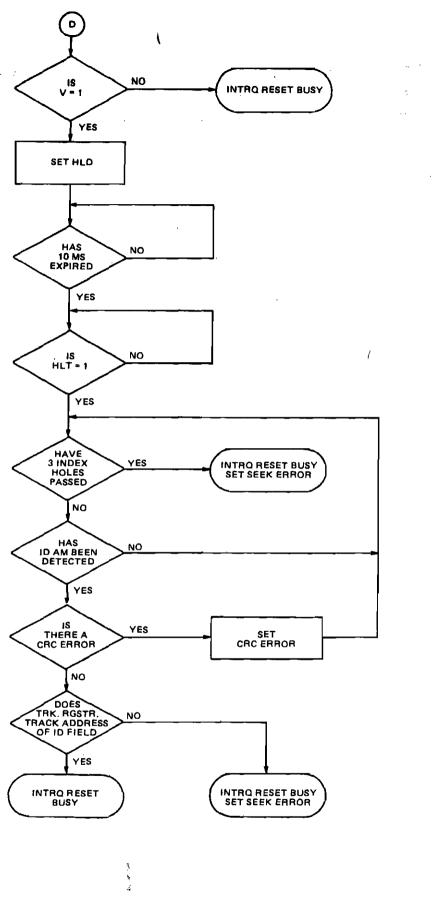

| 4.2.1.5   | Type I Commands                          | 4-30      |

| 4.2.1.6   | Type II Commands                         | 4-35      |

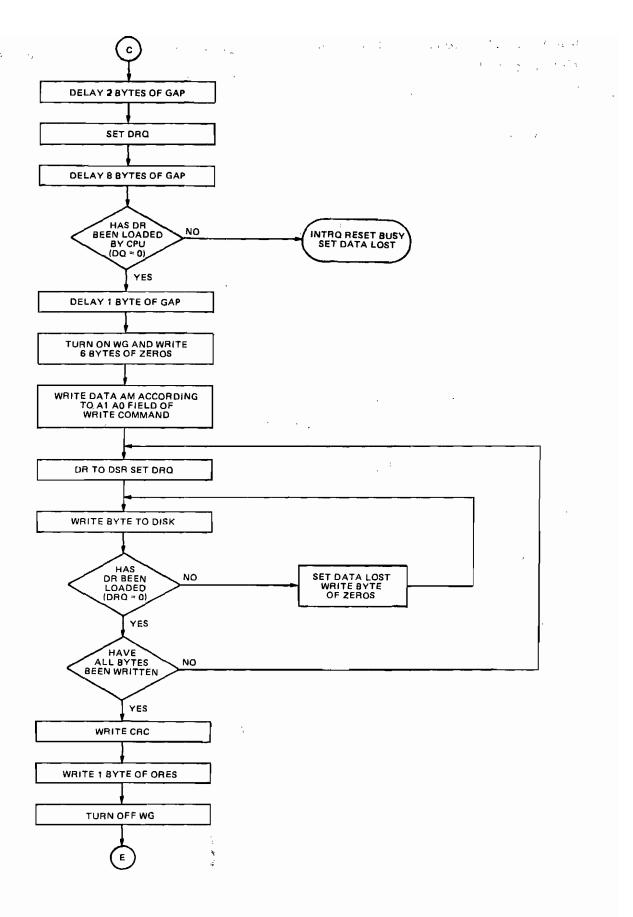

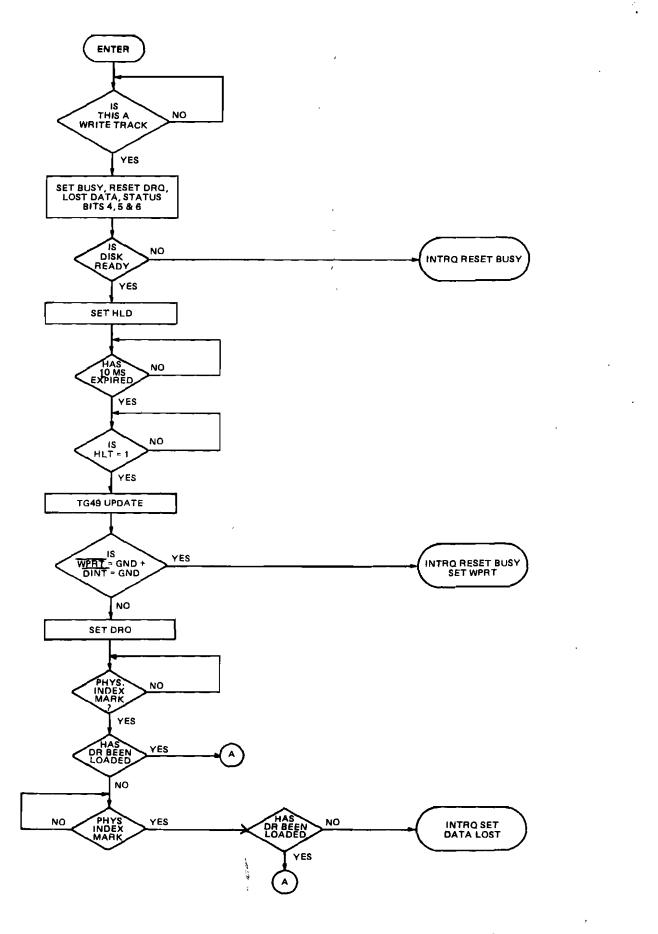

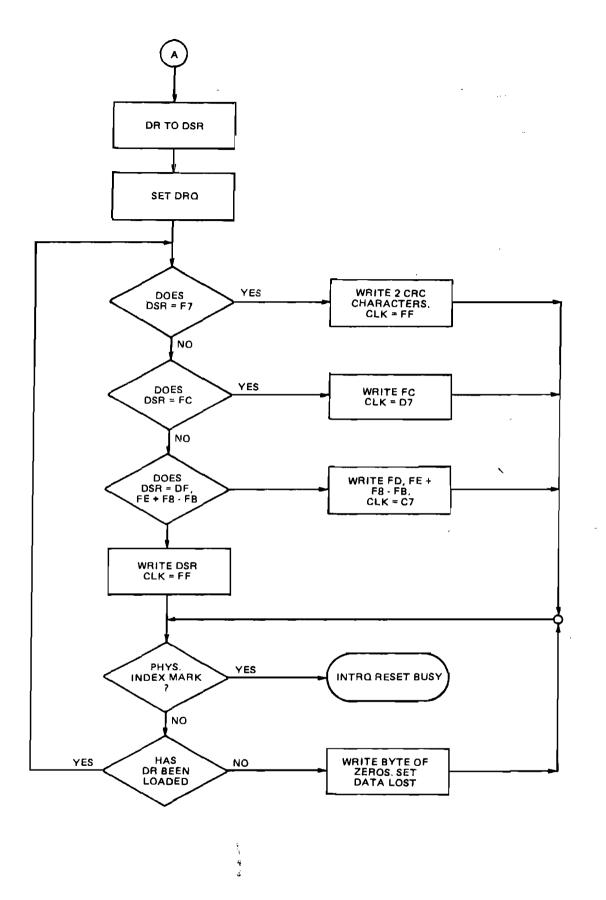

| 4.2.1.7   | Type III Commands                        | 4 - 43    |

| 4.2.1.8   | Type IV Commands                         | 4 - 47    |

| 4.2.1.9   | Status Description                       | 4-48      |

| 4.2.1.10  | Formatting the Disk                      | 4-51      |

| 4.2.1.11  | Timing Characteristics                   | 4-54      |

|           | •                                        |           |

,

۹.

| | |

ii

۲ :

# Paragraph

. •

ļ

· 7

Page

1

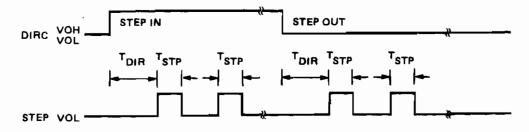

| 4.2.2  | Synchronous Up/Down Counter with Dual Clock |

|--------|---------------------------------------------|

|        | (U5, U6, U7, U8, U18, U19, U20, U21) 4-60   |

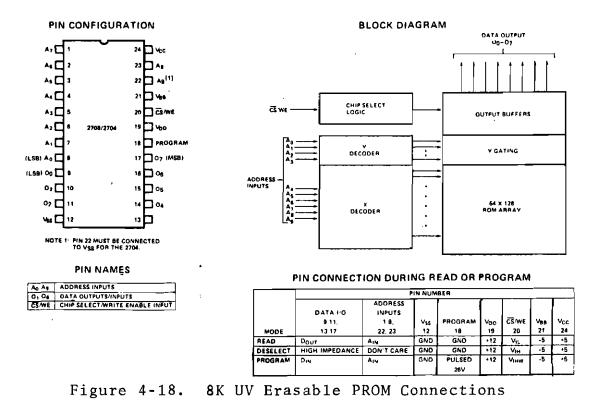

| 4.2.3  | 8K UV Erasable PROM (U48) 4-64              |

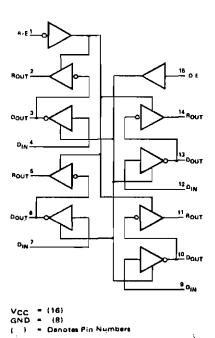

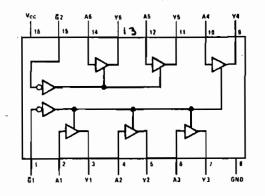

| 4.2.4  | Tri-State Quad Bus Transceiver (U37, U38,   |

|        | U50, U51)                                   |

| 4.2.5  | Tri-State Octal Buffers (U36) 4-67          |

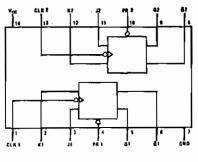

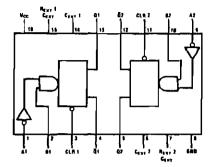

| 4.2.6  | Dual J-K Negative-Edge Triggerred Flip-     |

|        | Flops with Preset (U16, U17, U26, U41) 4-67 |

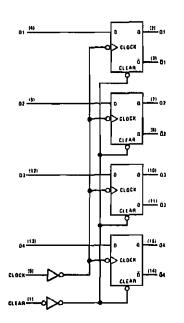

| 4.2.7  | Quad D Flip-Flops with Clear (U9, U22) 4-68 |

| 4.2.8  | Dual Retriggerable One-Shots with Clear     |

|        | (U15)                                       |

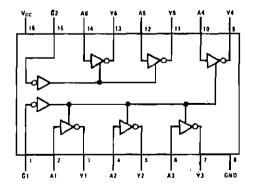

| 4.2.9  | Hex Tri-State Buffers (U25) 4-69            |

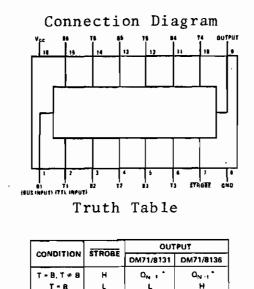

| 4.2.10 | Bus Comparator (U45, U47) 4-70              |

| 4.2.11 | Tri-State Buffers (U24, U30, U31, U42,      |

|        | U49, U53, U54)                              |

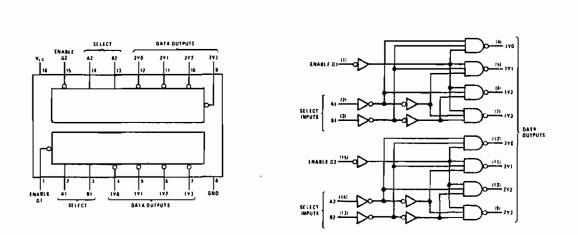

| 4.2.12 | Decoder/Demultiplexer (U33) 4-72            |

|        |                                             |

|        | SECTION 5 MAINTENANCE                       |

| 5.0    | Introduction                                |

| 5.1    | Circuit Board Checkout 5-1                  |

| 5.2    | Troubleshooting Procedures 5-2              |

| 5.2.1  | Complete AM-200 Failure                     |

| 5.2.2  | Partial Failure                             |

| 5.3    | Warranty Procedures                         |

|        |                                             |

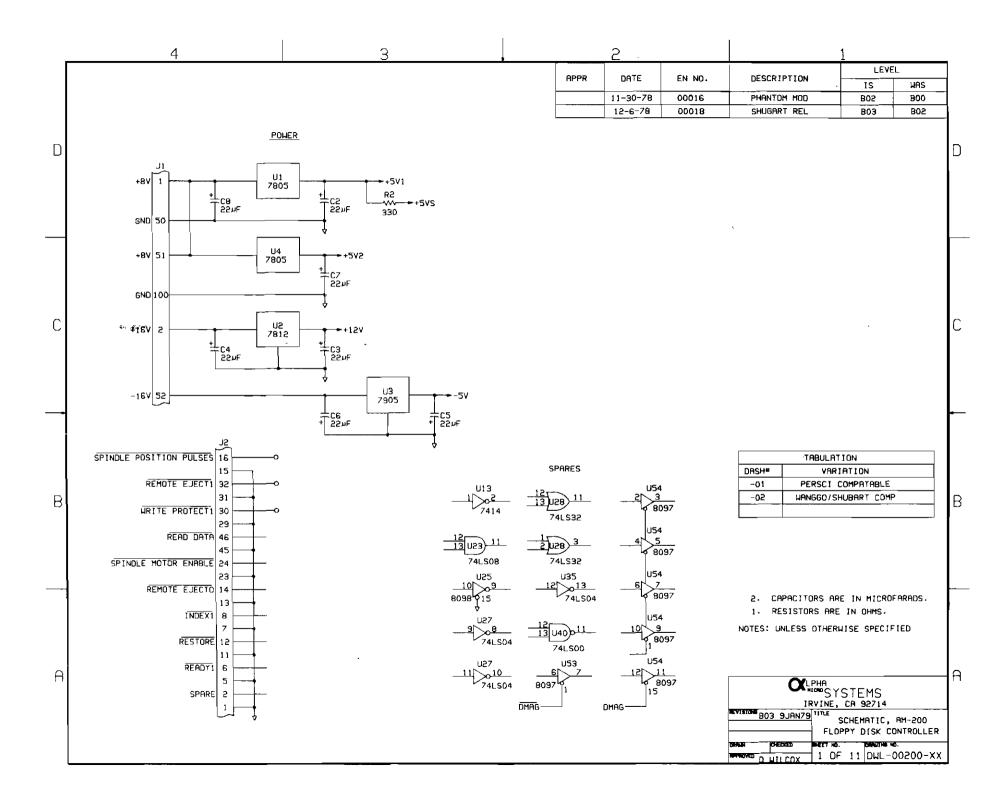

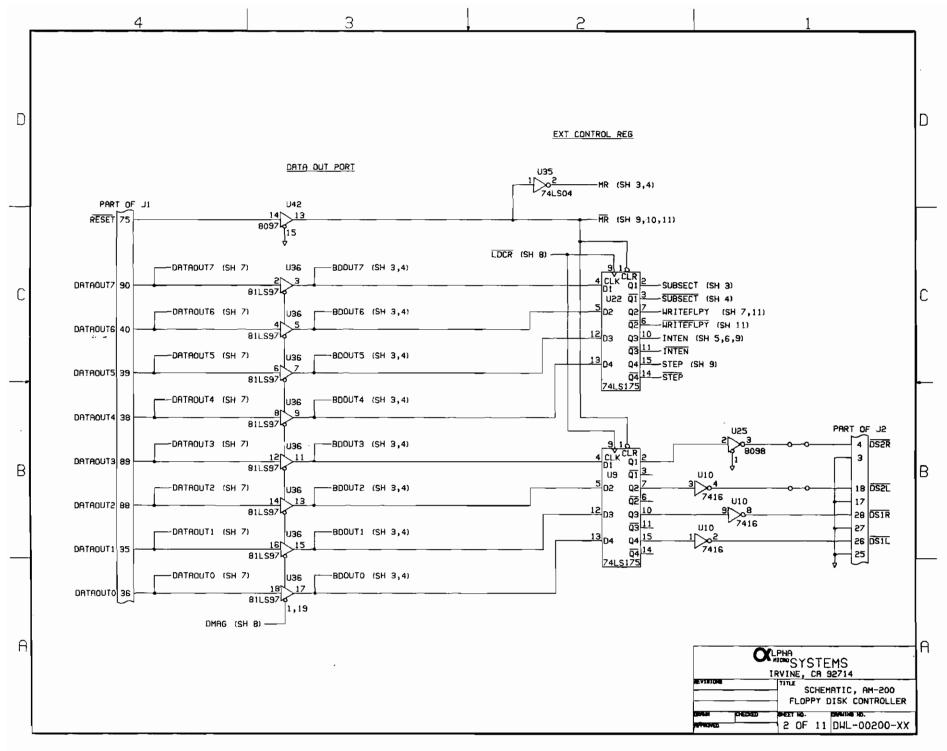

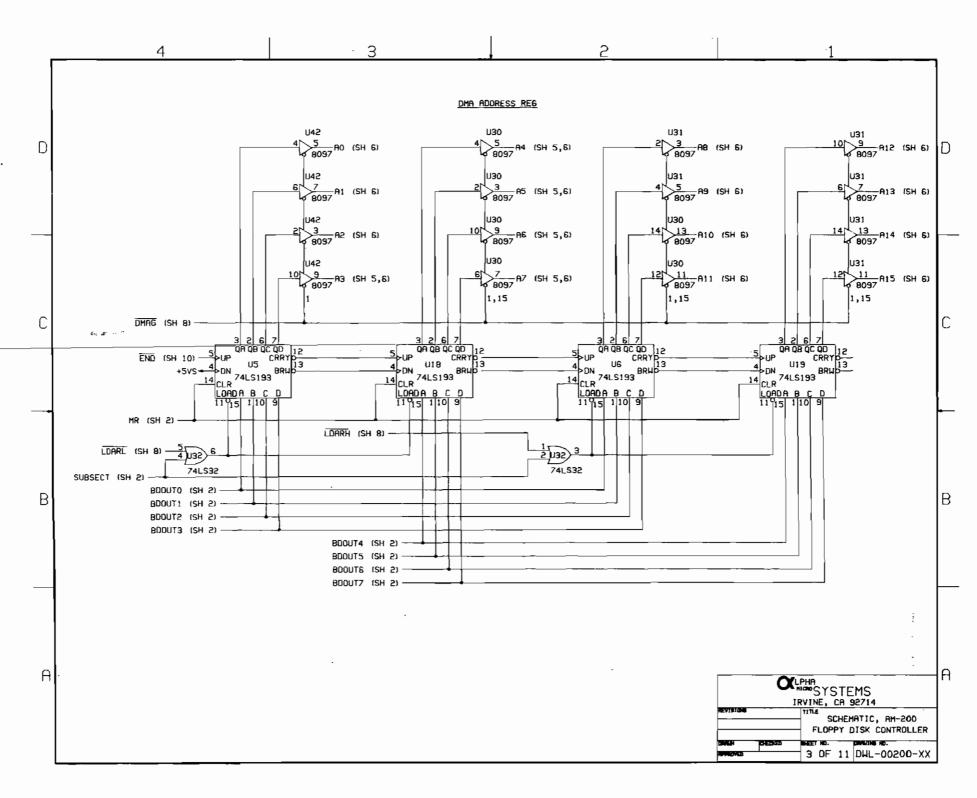

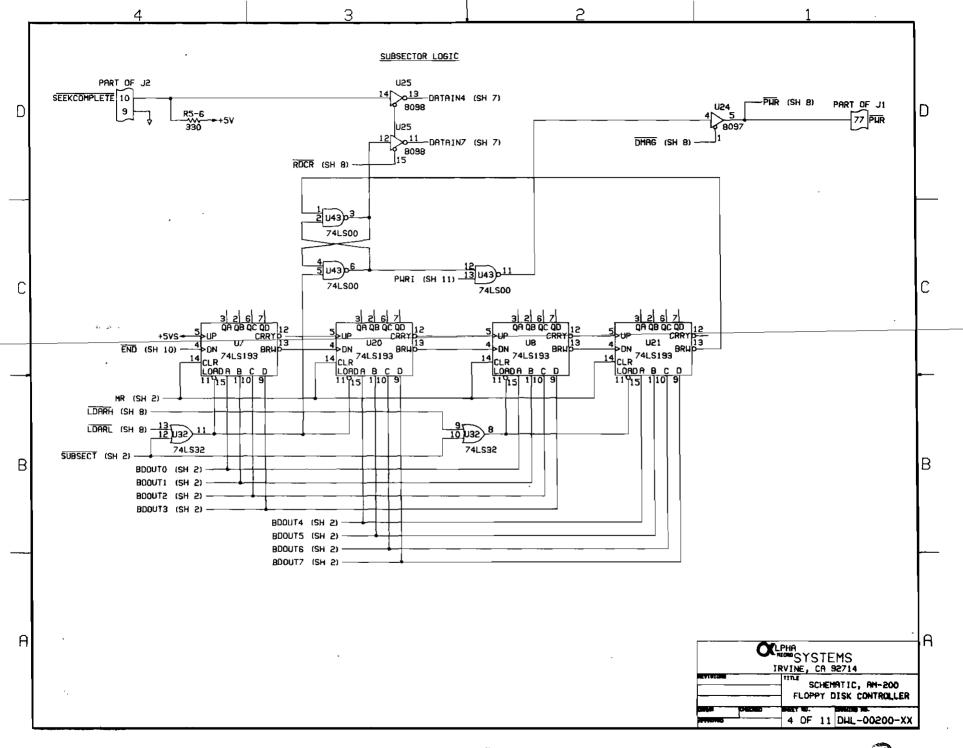

|        | SECTION 6 SCHEMATIC AND PARTS LIST          |

|        | Schematic and Parts List 6-1                |

٦ ;

## LIST OF ILLUSTRATIONS

# Figure

## Page

e.ľ

۰.,

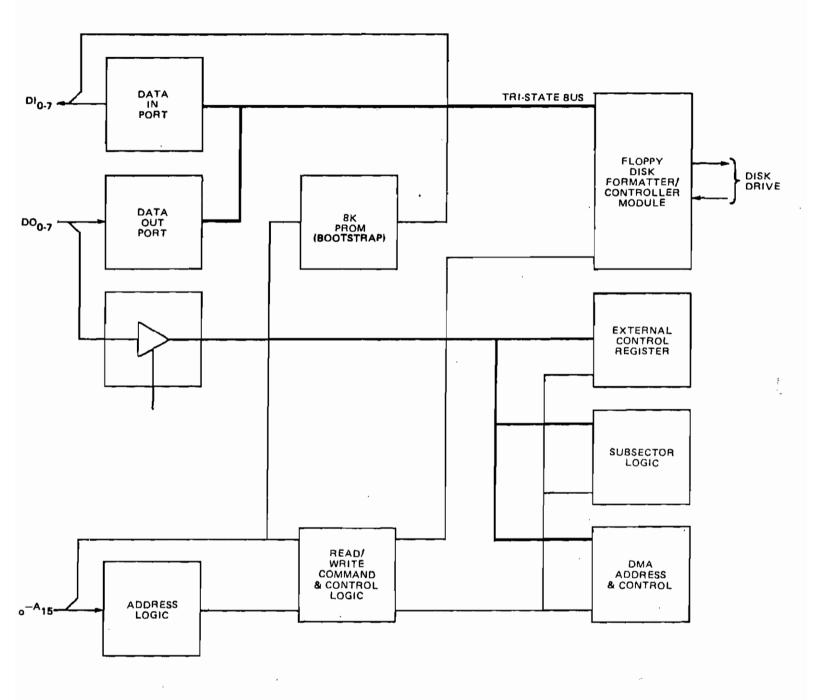

| 1-1    | AM-200 Simplified Block Diagram 1-2                                 |

|--------|---------------------------------------------------------------------|

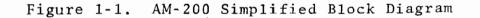

| 2-1    | AM-200 Cabling to PERSCI Disk Drive 2-13                            |

| 2-2    | PERSCI Dual Disk Drive Wiring Modifications. 2-14                   |

| 2-3    | AM-200 Circuit Board Layout                                         |

| 2 - 4  | Jumpers for Use with AM-100 System 2-18                             |

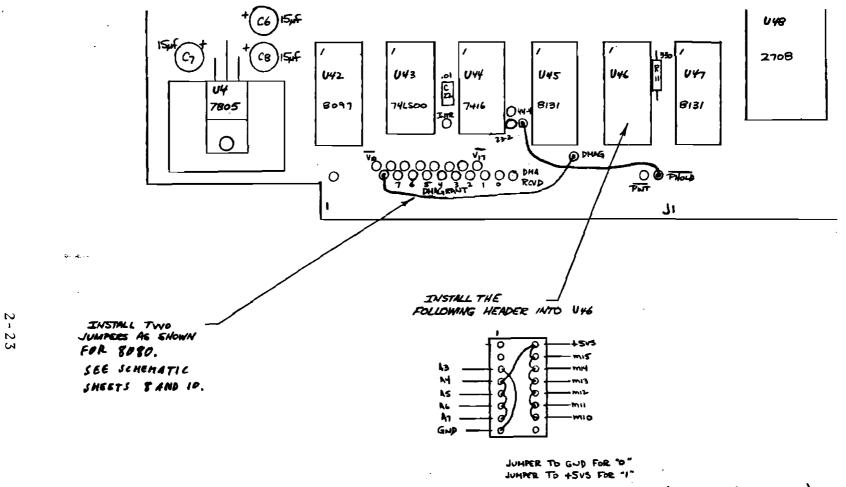

| 2-5    | Jumpers for Use with 8080 System 2-23                               |

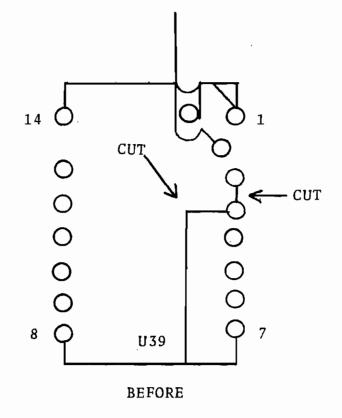

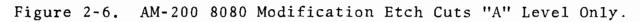

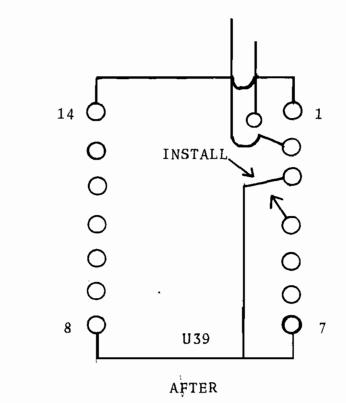

| 2-6    | AM-200 8080 Modification Etch Cuts "A"                              |

|        | Level Only                                                          |

| 2-7    | AM-200 8080 Modification Wire Additions "A"                         |

|        | Level Only                                                          |

| 4 - 1  | AM-200 Functional Block Diagram 4-3                                 |

| 4 - 2  | Disk Read and Write Sequence Flow Diagram . 4-13                    |

| 4 - 3  | Floppy Disk Formatter/Controller Pin                                |

|        | Connections                                                         |

| 4 - 4  | Floppy Disk Formatter/Controller Module                             |

|        | Block Diagram 4-21                                                  |

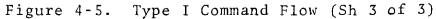

| 4 - 5  | Type I Command Flow 4-31                                            |

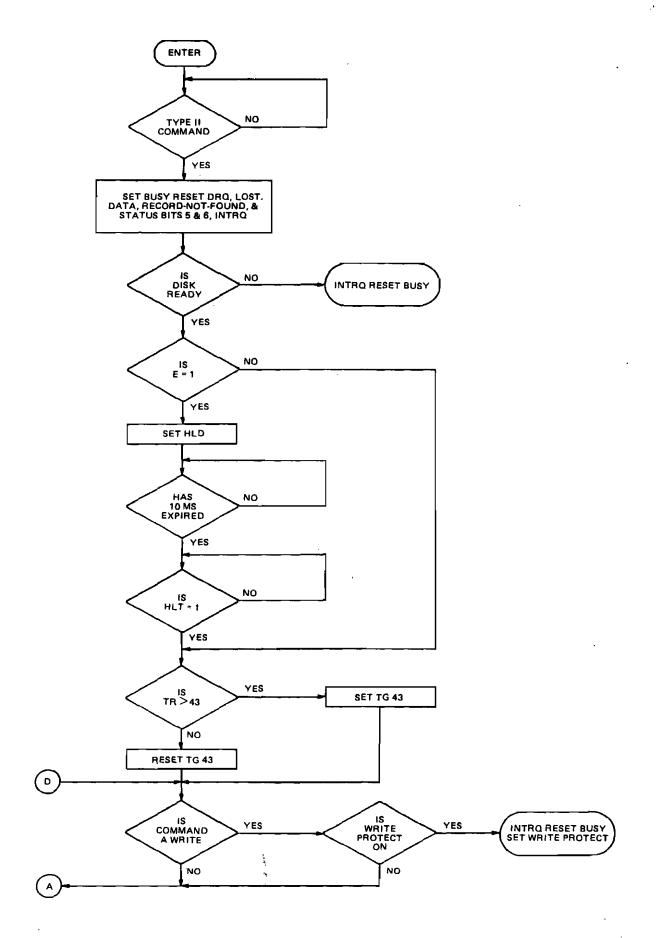

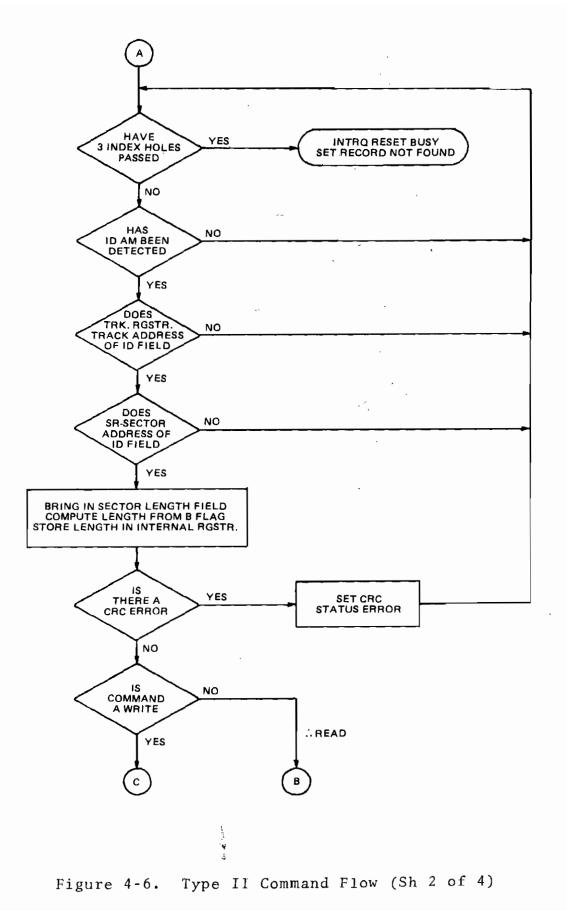

| 4-6    | Type II Command Flow 4-36                                           |

| 4 - 7  | Type III Command Flow 4-44                                          |

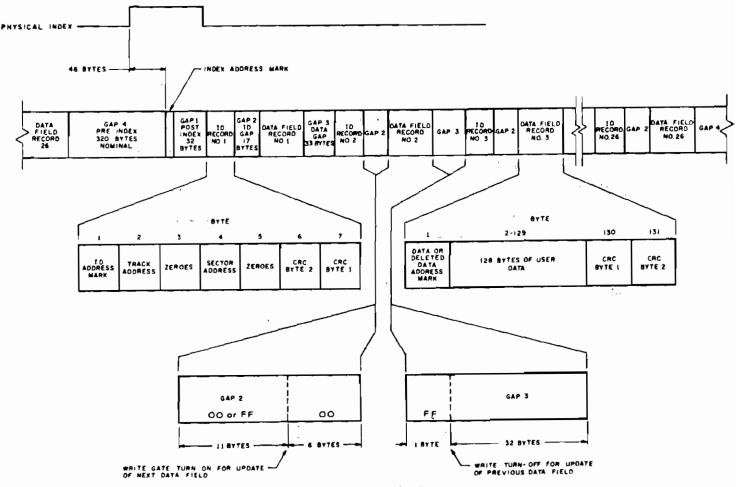

| 4 - 8  | Track Format                                                        |

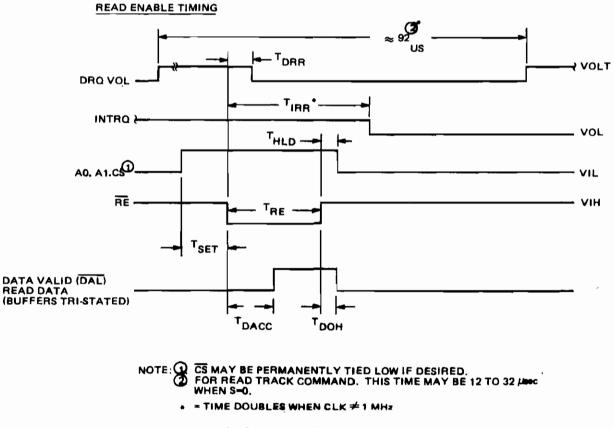

| 4-9    | Read Operations Timing 4-54                                         |

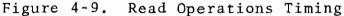

| 4-10   | Write Operations Timing 4-55                                        |

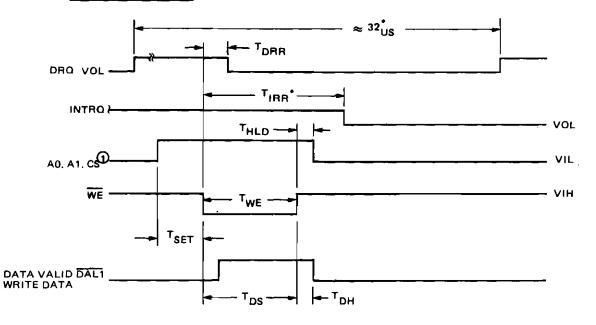

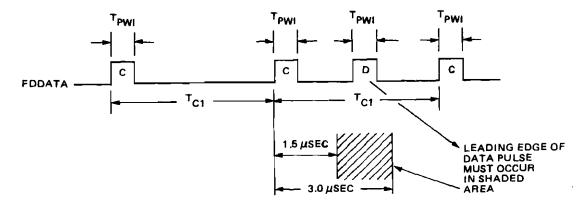

| 4-11   | External Data Separation Timing $(\overline{\text{XTDS}}=0)$ 4-56   |

| 4 - 12 | Internal Data Separation Timing ( $\overline{\text{XTDS}}$ =1) 4-57 |

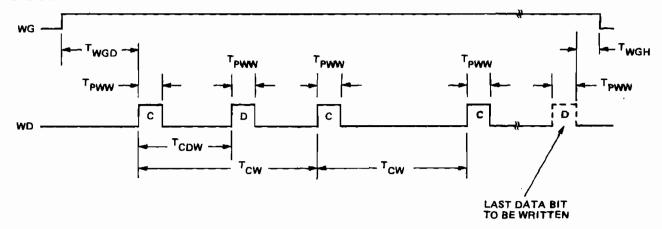

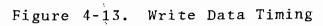

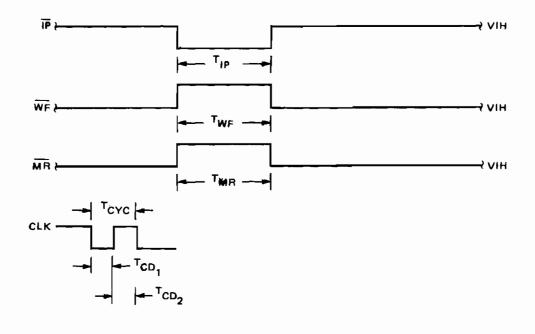

| 4-13   | Write Data Timing 4-58                                              |

| 4-14   | Miscellaneous Timing 4-59                                           |

|        |                                                                     |

# LIST OF ILLUSTRATIONS (Cont.)

`

# Figure

Page

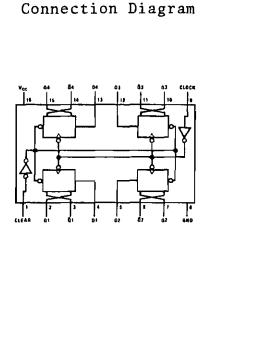

| 4-15    | Synchronous Up/Down Counter Connections 4-61      |

|---------|---------------------------------------------------|

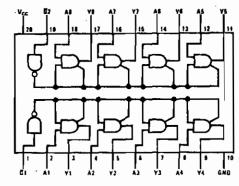

| 4-16    | Synchronous Up/Down Counter Logic Diagram 4-62    |

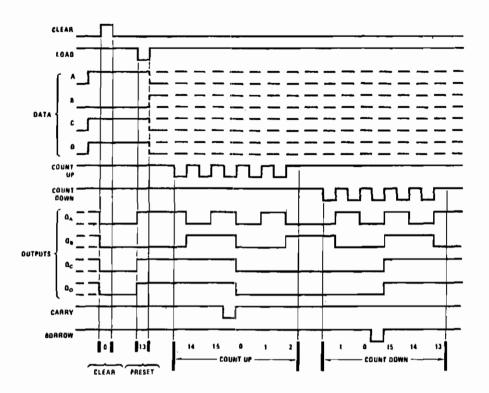

| 4-17    | Synchronous Up/Down Counter Timing Diagram . 4-63 |

| 4-18    | 8K UV Erasable PROM Connections 4-64              |

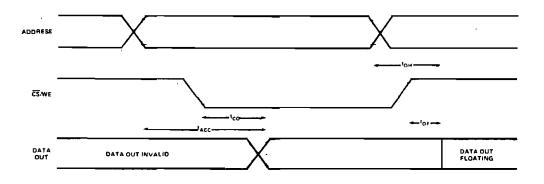

| 4-19    | 8K UV Erasable PROM Timing 4-64                   |

| 4 - 20  | Tri-State Bus Transceiver Connections 4-66        |

| 4-21    | Tri-State Octal Buffer Connections 4-67           |

| 4-22    | J-K Flip-Flop Connections 4-67                    |

| 4 - 23  | Quad D Flip-Flop Connections 4-68                 |

| 4 - 2 4 | One-Shot Connections 4-69                         |

| 4 - 2 5 | Hex Tri-State Buffer Connections 4-69             |

| 4-26    | Bus Comparator Connections 4-70                   |

| 4 - 27  | Tri-State Buffer Connections 4-71                 |

| 4 - 2 8 | Decoder/Demultiplexer Connections 4-72            |

v

, ;

## LIST OF TABLES

# <u>Table</u>

Page

• -

6

|       | · ,                                               |

|-------|---------------------------------------------------|

| 2-1   | AM-200 Specifications                             |

| 2 - 2 | S-100 Bus Interface Signals List 2-3              |

| 2 - 3 | AM-200 Floppy Disk Interface Signals List . 2-8   |

| 3-1   | I/O Port Definitions                              |

| 3-2   | External Control Register Data                    |

| 3-3   | External Status Register Data                     |

| 4-1   | AM-200 Circuit Board Signal List 4-5              |

| 4 - 2 | Floppy Disk Formatter/Controller Signal List 4-16 |

| 4 - 3 | AM-200 Register Addresses 4-19                    |

| 4 - 4 | Stepping Rates                                    |

| 4 - 5 | Command Summary 4-28                              |

| 4 - 6 | Flag Summary                                      |

| 4 - 7 | Control Bytes for Initialization 4-47             |

| 4 - 8 | Status Register Summary 4-48                      |

| 4 - 9 | Status Bits for Type I Commands 4-49              |

| 4-10  | Status Bits for Type II and III Commands 4-50     |

|       |                                                   |

vi

۱ ;

| USER COMMENTS                         | TECHNICAL PUBLICATIONS FILE REFERENCE                        |

|---------------------------------------|--------------------------------------------------------------|

|                                       |                                                              |

| FROM: NAME                            | \                                                            |

|                                       | NOTE: Use this form to communicate any errors                |

|                                       | suggested changes, or general comments a bout this document. |

| ADDRESS                               | If necessary, call us at:                                    |

| CITY                                  | (714) 957-6076                                               |

|                                       |                                                              |

| STATEZIP                              |                                                              |

|                                       |                                                              |

|                                       |                                                              |

| DOCUMENT: TITLE/NUMBER/REVISION       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

| COMMENTS:                             |                                                              |

|                                       |                                                              |

| ·                                     |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

| · · · · · · · · · · · · · · · · · · · |                                                              |

|                                       | · · · · · · · · · · · · · · · · · · ·                        |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       | ······                                                       |

|                                       | · · · · · · · · · · · · · · · · · · ·                        |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

|                                       |                                                              |

۰.

## SECTION 1 GENERAL DESCRIPTION

#### 1.0 INTRODUCTION.

This manual provides operating and maintenance instructions for the AM-200 Floppy Disk Controller Circuit Board manufactured by Alpha Microsystems located in Irvine, California. Circuit board description, operating and usage instructions, programming, theory of operation, and maintenance instructions are included to provide the user with the information necessary to utilize this circuit board to its full capability.

ł

#### 1.1 CIRCUIT BOARD DESCRIPTION.

The AM-200 Floppy Disk Controller circuit board is an S-100 bus compatible DMA floppy disk controller based on the Western Digital FD 1771 control DIP. It provides full or partial sector reading from the drive and has multiple drive control and multi-level interrupt capabilities. An 8K PROM is contained on the board to provide a bootstrap load program for the floppy disk subsystem.

A simplified block diagram of the circuit board is shown in Figure 1-1. For a complete detailed description of circuit board operation, see Section 4 of this manual.

#### **1.2** APPLICATION.

This circuit board provides the data processing necessary for control and operation of most popular single density floppy disk drives in an S-100 bus system. The AM-200 requires separate clock and data inputs and provides outputs for step-direction drives. See Section 2 of this manual for wiring instructions and system interface information.

.

## SECTION 2 OPERATING DATA

2.0 INTRODUCTION.

This section contains information on the use of the AM-200 Floppy Disk Controller Board. Capabilities, specifications, interface wiring and user option descriptions are provided for the successful integration of the board into the user's system.

2.1 CAPABILITIES AND SPECIFICATIONS.

This circuit board operates from the standard S-100 bus structure and provides interface capability to most popular single density floppy disk drives. It is a DMA device for transfer of data between a floppy disk drive and system memory under CPU control. Specifications for the AM-200 circuit board are contained in Table 2-1.

# Table 2-1. AM-200 Specifications

· • •

C

۲

·

| Parameter         | Specifications                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface         | S-100 Bus for CPU, a maximum of four<br>floppy disk drives with separate clock<br>and data inputs and with step-direction<br>head positioning. |

| Bootstrap Program | Eight by 1024 bit PROM which contains bootstrap program.                                                                                       |

| Interrupts        | Multiple level interrupt capability - user selected.                                                                                           |

| DMA Access        | Multiple level direct memory access -<br>user selected.                                                                                        |

| Data Transfer     | Full DMA transfer of data between floppy drive and system memories.                                                                            |

| Sector Read       | Full or partial sector read from floppy drive.                                                                                                 |

| Circuit Board     | Standard 5" x 10" with 100 pin connector.                                                                                                      |

1

## 2.2 INTERFACE DESCRIPTION AND WIRING.

The AM-200 Floppy Disk Controller provides interface capability between the standard S-100 bus and floppy disk drives.

### 2.2.1 S-100 BUS INTERFACE.

The AM-200 circuit board is fully S-100 bus compatible. The board and its associated floppy disk drives are addressed through the address lines and data is transferred through the standard data in and data out lines. The S-100 bus connections are made via the bottom edge connector and are described in Table 2-2.

### 2.2.2 FLOPPY DRIVE INTERFACE.

The AM-200 Floppy Disk controller accommodates a maximum of four floppy disk drives. Most of the popular drives are compatible if they provide outputs of separate clock and data and require step-direction head control. All floppy disk drive interface signals are described in Table 2-3.

| MNEMONIC | NAME            | PIN | DESCRIPTION                                                         |

|----------|-----------------|-----|---------------------------------------------------------------------|

| ADDSBL   | Address Disable | 22  | AM-200 output to<br>disconnect CPU address<br>lines from S-100 bus. |

| A0       | Address 0       | 79  | 16 Bits of S-100                                                    |

| A1       | Address 1       | 80  | Addressing.                                                         |

| A2       | Address 2       | 81  | Addressing.                                                         |

| Á3       | Address 3       | 31  |                                                                     |

| A4       | Address 4       | 30  |                                                                     |

| A5 .     | Address 5       | 29  |                                                                     |

| A6       | Address 6       | 82  |                                                                     |

### Table 2-2. S-100 Bus Interface Signals List

۰.

| MNEMONIC  | NAME              | PIN | DESCRIPTION                                  |

|-----------|-------------------|-----|----------------------------------------------|

| A7        | Address 7         | 83  | 16 Bits of S-100                             |

| A8        | Address 8         | 84  | Addressing.                                  |

| A 9       | Address 9         | 34  |                                              |

| A10       | Address 10        | 37  |                                              |

| A11       | Address 11        | 87  |                                              |

| A12       | Address 12        | 33  |                                              |

| A13       | Address 13        | 85  |                                              |

| A14       | Address 14        | 86  |                                              |

| A15       | Address 15        | 32  |                                              |

| CCDSBL    | Control Disable   | 19  | AM-200 output to dis-<br>connect CPU control |

|           |                   |     | lines from S-100 bus.                        |

| DATAIN 0  | Input Data Bit O  | 95  | Data Input Port.                             |

| DATAIN 1  | Input Data Bit 1  | 94  | Bus Master Input                             |

| DATAIN 2  | Input Data Bit 2  | 41  | From Slaves.                                 |

| DATAIN 3  | Input Data Bit 3  | 42  |                                              |

| DATAIN 4  | Input Data Bit 4  | 91  |                                              |

| DATAIN 5  | Input Data Bit 5  | 92  |                                              |

| DATAIN 6  | Input Data Bit 6  | 93  |                                              |

| DATAIN 7  | Input Data Bit 7  | 43  |                                              |

| DATAOUT 0 | Output Data Bit O | 36  | Data Output Port.                            |

| DATAOUT 1 | Output Data Bit 1 | 35  | Bus Master Output                            |

| DATAOUT 2 | Output Data Bit 2 | 88  | To Slaves.                                   |

| DATAOUT 3 | Output Data Bit 3 | 89  |                                              |

| DATAOUT 4 | Output Data Bit 4 | 38  |                                              |

| DATAOUT 5 | Output Data Bit 5 | 39  |                                              |

| DATAOUT 6 | Output Data Bit 6 | 40  |                                              |

| DATAOUT 7 | Output Data Bit 7 | 90  |                                              |

| MNEMONIC   | NAME                                                    | PIN | DESCRIPTION                                                                                                                         |

|------------|---------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| DMAGRANT 0 | Direct Memory Access<br>Grant O                         | 63  | Input from CPU indicating                                                                                                           |

|            | Direct Memory Access<br>Grant 1                         | 62  | bus control has been<br>relinquished to one of                                                                                      |

|            | Direct Memory Access<br>Grant 2                         | 61  | 8 DMA controllers.<br>Any one of 8 is                                                                                               |

|            | Direct Memory Access<br>Grant 3                         | 60  | selectable by jumper<br>on AM-200 board.<br>Normal level is 6 for                                                                   |

|            | Direct Memory Access<br>Grant 4<br>Direct Memory Access | 59  | floppy controller.                                                                                                                  |

|            | Grant 5<br>Direct Memory Access                         | 58  |                                                                                                                                     |

|            | Grant 6<br>Direct Memory Access                         | 57  |                                                                                                                                     |

|            | Grant 7                                                 | 56  |                                                                                                                                     |

| DMARCVD    | DMA Received                                            | 64  | DMA acknowledge signal from<br>CPU, jumper selectable<br>on AM-200 board. Signal<br>indicates DMAGRANT is<br>coming the next cycle. |

| DODSBL     | Data Out Disable                                        | 23  | AM-200 output to disconnect<br>CPU data lines from S-100<br>bus.                                                                    |

| PDBIN      | Data Bus In                                             | 78  | Read enable. Used by bus<br>master to request addressed<br>slave to place data on<br>input port.                                    |

2 - 5

靜

ſ .

1

| MNEMONIC | NAME              | PIN | DESCRIPTION                                                                                                                            |

|----------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| PHLDA    | Halt Acknowledge  | 26  | AM-200 input, jumper selec-<br>table. Indicates that the<br>CPU has halted and its<br>output lines are discon-<br>nected from the bus. |

| PHOLD    | CPU Halt          | 74  | Halts the CPU for Direct<br>Memory Access control<br>(Jumper Selectable).                                                              |

| PINT     | Interrupt Request | 73  | ( <u>INTREQ</u> ) Jumper selectable<br>interrupt request output.                                                                       |

| PINTE    | Interrupt Enable  | 28  | (INTE) AM-200 output to<br>hold Interrupt Enable bus<br>signal low during DMA.                                                         |

| РКДҮ     | Ready             | 72  | AM-200 I/O signal to allow extensions of bus timing.                                                                                   |

| PSYNC    | Sync              | 76  | Indicates the beginning<br>of each bus transfer cycle.                                                                                 |

| PWAIT    | Wait              | 27  | Acknowledges that the CPU has stopped.                                                                                                 |

| PWR      | Write Strobe      | 77  | Write strobe. Generated<br>by bus masters as write<br>command to slaves.                                                               |

| RESET    | Reset             | 75  | AM-200 Reset input.                                                                                                                    |

÷

٠

.

.

•

| MNEMONIC | NAME                              | PIN | DESCRIPTION                                                                    |

|----------|-----------------------------------|-----|--------------------------------------------------------------------------------|

| SHLTA    | Halt                              | 48  | (HLTA) AM-200 output to<br>hold Halt acknowledge bus<br>signal low during DMA. |

| SINP     | I/O Input Cycle                   | 46  | AM-200 I/O signal indica-<br>ting I/O input operation.                         |

| SINTA    | Interrupt Acknowledge             | 96  | (INTA) AM-200 output to<br>hold SINTA bus signal low<br>during DMA.            |

| SMEMR    | Memory Read Cycle                 | 47  | AM-200 I/O signal indica-<br>ting memory read operation.                       |

| SMI      | Memory Instruction<br>Fetch Cycle | 44  | AM-200 output to hold SMI<br>bus signal low during DMA.                        |

| SOUT     | I/O Output Cycle                  | 45  | AM-200 I/O signal indica-<br>ting I/O output operation.                        |

| SSTACK   | Stack Operation                   | 98  | AM-200 output to hold<br>SSTACK bus signal low<br>during DMA.                  |

| STDSBL   | Status Disable                    | 18  | AM-200 output to dis-<br>connect CPU status lines<br>from S-100 bus.           |

| SWO      | Write Cycle                       | 97  | AM-200 I/O signal indi-<br>cating output operation.                            |

| MNEMONIC                                                                                                                                                      | NAME                                                                                                                 | PIN                                    | DESCRIPTION                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| $     \overline{VI0}     \overline{V11}     \overline{V12}     \overline{V13}     \overline{V14}     \overline{V15}     \overline{V16}     \overline{V17}   $ | Interrupt 0<br>Interrupt 1<br>Interrupt 2<br>Interrupt 3<br>Interrupt 4<br>Interrupt 5<br>Interrupt 6<br>Interrupt 7 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | Jumper selected<br>Interrupts. Used for both<br>interrupt requests and<br>DMA requests. Normal<br>configuration: VI6 used<br>for DMA request. |

| ø2                                                                                                                                                            | Phase 2 clock                                                                                                        | 24                                     | Phase 2 clock from cpu.                                                                                                                       |

| +8VDC                                                                                                                                                         | +8VDC                                                                                                                | 1,51                                   | +8V power.                                                                                                                                    |

| +16VDC                                                                                                                                                        | +16VDC                                                                                                               | 2,52                                   | +16 power.                                                                                                                                    |

| GND                                                                                                                                                           | Ground                                                                                                               | 50,                                    | System Ground<br>100                                                                                                                          |

Table 2-2 (Cont.). S-100 Bus Interface Signals List

)

۰.

ť

Table 2-3. AM-200 Floppy Disk Interface Signals List

| MNEMONIC | NAME                        | PIN      | DESCRIPTION                                                                        |

|----------|-----------------------------|----------|------------------------------------------------------------------------------------|

| DSIL     | Drive Select 1 Left<br>Rtn  | 26<br>25 | Low level output loads and<br>selects Head 0 (The left-<br>side head) of drive 1.  |

| DSIR     | Drive Select 1 Right<br>Rtn | 28<br>27 | Low level output loads and<br>selects Head 1 (the right-<br>side head) of drive 1. |

| DS 2L    | Drive Select 2 Left<br>Rtn  | 18<br>17 | Low level output loads and<br>selects Head 0 (the left-<br>side head) of drive 2.  |

Table 2-3 (Cont.) AM-200 Floppy Disk Interface Signals List

| MNEMONIC  | NAME                        | PIN        | DESCRIPTION                                                                                                                                                                                                     |

|-----------|-----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS2R      | Drive Select 2 Right<br>Rtn | 4<br>3     | Low level output loads and<br>selects Head 1 (the right-<br>side head) of drive 2.                                                                                                                              |

| INDEX     | Disk Index O<br>Rtn         | 20<br>19   | AM-200 input. One ms nega-<br>tive going pulse occurs for<br>each revolution of the<br>selected disk.                                                                                                           |

| INDEX 1   | Disk Index 1<br>Rtn         | 8<br>7     | AM-200 input. Optional<br>index pulse. (No connec-<br>tion in AM-200).                                                                                                                                          |

| INWARDS   | Direction Select<br>Rtn     | 34<br>33   | AM-200 output. Defines di-<br>rection of motion of the<br>head positioner when the<br>step line is pulsed. Low =<br>inward (higher track number).<br>High = outward (lower track<br>number - away from center). |

| READ DATA | Disk Output Data<br>Rtn     | 46<br>45   | AM-200 input. Data output<br>of selected head. Each flux<br>transition = 200 ns pulse<br>active low. (No connection<br>in AM-200.)                                                                              |

| READY     | Ready 0<br>Rtn              | 22<br>· 21 | AM-200 input. A low level<br>indicates that a diskette<br>is loaded in selected drive<br>and is within 90% of its<br>operating speed.                                                                           |

Table 2-3 (Cont.). AM-200 Floppy Disk Interface Signals List

| MNEMONIC                   | NAME                             | PIN      | DESCRIPTION                                                                                              |

|----------------------------|----------------------------------|----------|----------------------------------------------------------------------------------------------------------|

| READY 1                    | Ready 1<br>Rtn                   | 6<br>5   | AM-200 input. Optional<br>ready signal. (No connec-<br>tion in AM-200.)                                  |

| REMOTE<br>EJECT 0          | Remote Eject O<br>Rtn            | 14<br>13 | Low level ejects diskette<br>in selected drive. (No<br>connection in AM-200.)                            |

| REMOTE<br>EJECT 1          | Remote Eject 1<br>Rtn            | 32<br>31 | Optional remote eject<br>signal. (Jumper pad in<br>AM-200.)                                              |

| RESTORE                    | Restore Head to 00<br>Rtn        | 12<br>11 | Low level causes low speed<br>repositioning of the heads<br>to track 00. (No connec-<br>tion in AM-200.) |

| SEEK<br>COMPLETE           | Seek Operation Com-<br>plete Rtn | 10<br>9  | AM-200 input. Low level<br>indicates that a seek or<br>restore operation has been<br>completed.          |

| SEPCLOCK                   | Separated Clock<br>Rtn           | 50<br>49 | AM-200 input. Separated data from read data.                                                             |

| SEPDATA                    | Separated Data<br>Rtn            | 48<br>47 | AM-200 input. Separated data from read data.                                                             |

| SPINDLE<br>MOTOR<br>ENABLE | Spindle Motor Enable<br>Rtn      | 24<br>23 | Low level energizes the<br>spindle motor. (No<br>connection in AM-200.)                                  |

# Table 2-3 (Cont.). AM-200 Floppy Disk Interface Signals List

| MNEMONIC                      | NAME                           | PIN      | DESCRIPTION                                                                                                                            |

|-------------------------------|--------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| SPINDLE<br>POSITION<br>PULSES | Spindle Position<br>Pulses Rtn | 16<br>15 | Jumper pad in AM-200                                                                                                                   |

| STEP                          | Step Pulses<br>Rtn             | 36<br>35 | AM-200 output. Low level<br>of one pulse for each<br>track crossed by the head<br>for a seek to a new address.                         |

| TRACK 0                       | Track 0<br>Rtn                 | 42<br>41 | AM-200 input. Low level<br>indicates heads are posi-<br>tioned over track 0.                                                           |

| WD                            | Write Data Rtn                 | 38<br>37 | AM-200 output. Write data<br>to disk. Write current<br>changes polarity for each<br>positive to negative tran-<br>sition on this line. |

| WG                            | Write Gate<br>Rtn              | 40<br>39 | AM-200 output. Low level<br>turns on write current.                                                                                    |

| WP                            | Write Protect<br>Rtn           | 44<br>43 | AM-200 input. Low level<br>indicates that the selected<br>disk is write protected.                                                     |

| WRITE<br>PROTECT 1            | Write Protect 1<br>Rtn         | 30<br>29 | Optional write protect line.<br>(Jumper pad in AM-200.)                                                                                |

#### 2.2.3 WIRING AND CONNECTIONS.

When the AM-200 circuit board is received, it is ready for use. No adjustment or calibration is required for operation. The hardware requirements for use are described in this section and the software requirements are described in Section 3.

First ensure that the proper power wiring is available and the correct voltages are connected to the various pins as shown on sheet 1 of the schematic. All power connections are made through the bottom edge connector.

All connections to the S-100 bus are made through the bottom edge connector (Table 2-2) and connections to the floppy disk drive are made through the top edge connector (Table 2-3). Ensure that these connections are correct before plugging the AM-200 circuit board into the system.

#### 2.2.3.1 AM-200 WITH PERSCI DRIVE.

When using the PERSCI drive and the IMS chassis, the fifty conductor cable must be positioned as shown in Figure 2-1. The edge connector for the AM-200 circuit board is connected so that the cable comes forward and back over the board to the rear of the computer chassis and connects to the PERSCI drive as shown. ŧ.

#### NOTE

Be sure to perform the wiring modifications to the PERSCI drive as shown in Figure 2-2 before turning on system.

2 A 8.

Figure 2-1. AM-200 Cabling to PERSCI Disk Drive

#### CAUTION

When installing cable at AM-200 end, make sure that pin 1 of the cable is nearest the edge of the circuit card. This is reversed from the standard marking on the flat cable connector on the board.

ý.

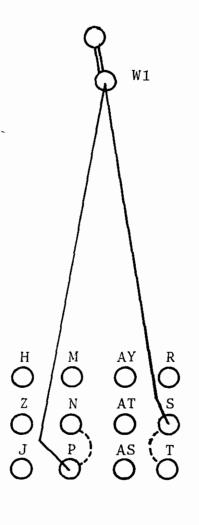

On the PC board near the rear of the PerSci drive, find the pattern as shown. 1. Remove N-P (shown dotted) 2. Remove S-T (shown dotted) 3. Add W1-P 4. Add W1-S

This modification must be made for each drive used.

When using more than one PerSci the following modification must be made on the 2nd dual drive.

Header U11

- 1. Remove 4-11 (shown dotted)

- 2. Remove 2-13 (shown dotted)

- 3. Add 4-9

- 4. Add 2-14

- Remove resistor pack on first drive.

Header U11 Second dual drive only

Figure 2-2. PERSCI Dual Disk Drive Wiring Modifications

2.2.3.2 AM-200 WITH WANGCO/ORBIS DRIVE.

When the AM-200 Floppy Disk Controller is used with Wangco/Orbis disk systems, the following modifications to the AM-200 are required. Use this procedure for modifications to Revision A and B boards.

<u>Modification Procedure.</u> Specific modification procedures are , as follows:

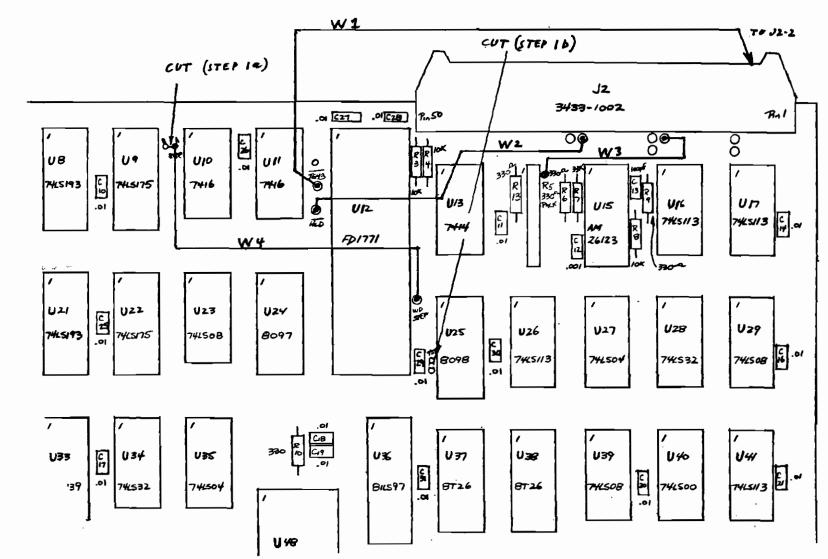

- Locate and cut the following traces as shown in Figure 2-3.

- a. On component side between U9 and U10, just opposite pin #2 of U10.

- b. On solder side between U12(1771) and U25. This is a very short, vertical trace just adjacent to pins 5 and 6 of U25.

- 2. Again on the solder side, add the following wires referring to the attached diagram.

- a. W1 from TG43 to J2-2. TG43 is just opposite pin

5 of U12(1771) and J2-2 is nearest to the right

edge of the PC board and the lower of the two pins.

- b. W2 from HLD to J2-30. HLD is just opposite U12-7 and J2-30 is just above U15-1.

- c. W3 from R5-2 to J2-16. R5-2 is the eyelet just above the "R5" symbol engraved on the PC board and J2-16 is just above U16-1.

- d. W4 from U10-2 to WD STEP. U10-2 is between U9 and U10 and is the hole closest to U10-2 and WD STEP is just adjacent to U12-27.

- 3. Perlod PROMS will not function with the Wangco system so you must order specific PROMS from Alpha Micro.

Figure 2-3. AM-200 Circuit Board Layout

۳۰۱.

の一方の

4. Due to differences between the Persci and the Wangco disk drives, an adapter board is supplied mounted in the disk drive cabinet. A cable must be connected between the connector marked "INTERFACE" and the AM-200. A Wangco system disk should also be included.

#### 2.3 USER OPTIONS.

Several features on the AM-200 circuit board can be jumper selected at the user's option. If these jumpers are desired, they must be inserted in the circuit board before it is installed in the system.

#### 2.3.1 ADDRESS CODE.

Circuit board addressing can be selected at the user's option for any address block on the address lines A3-A7. Address line A2 must be a zero to generate floppy controller enable (CE) and the first four addresses operate disk controller module registers (see paragraph 4.2.1.2). Connect jumper wires on header U46 to +5V and ground to assign the desired address block. The standard I/O address is: FO.

#### 2.3.2 INTERRUPT LINES.

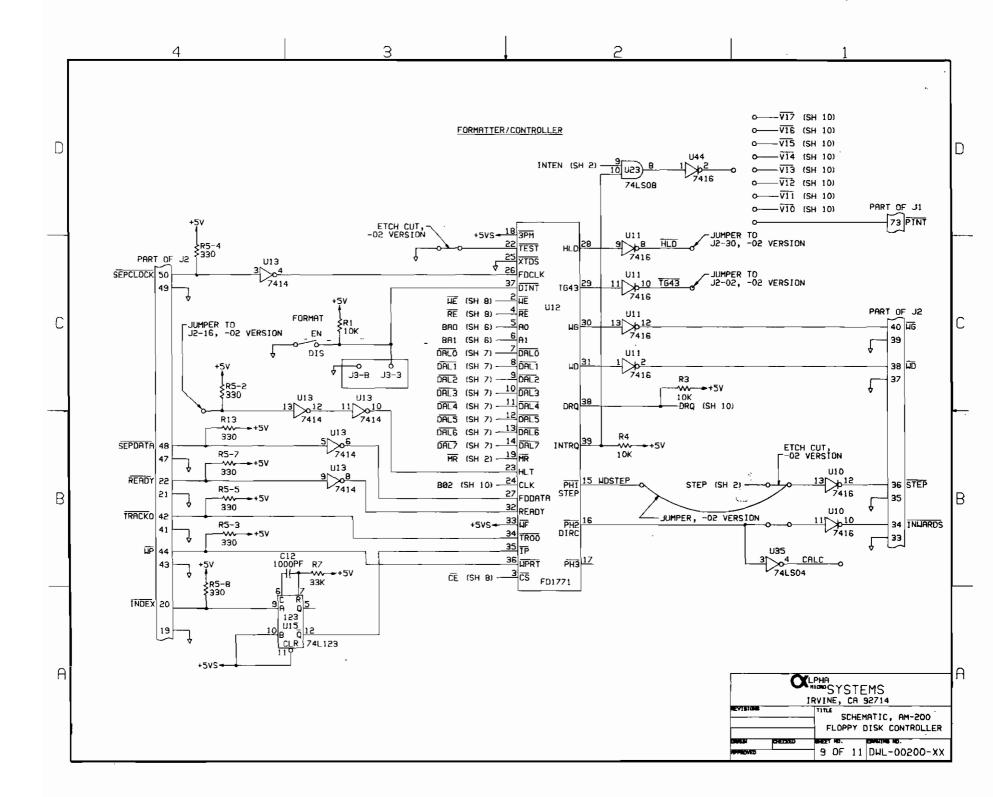

Interrupt compatibility for any S-100 bus system is provided with jumpers to PINT or any of the vectored interrupt lines VIO-VI7. Attach the jumper wire from the pad connected to pin 2 of U44 to the desired interrupt line (schematic sheet 9).

#### 2.3.3 DMA REQUEST LINES.

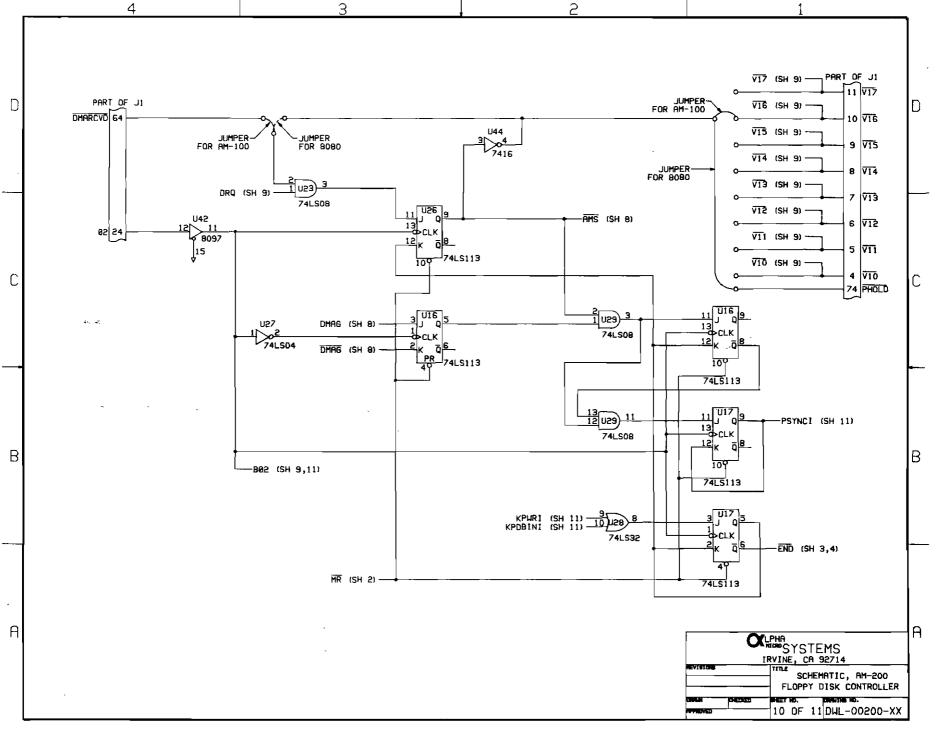

DMA request capability for any S-100 bus system is provided with jumpers to PHOLD or any of the vectored interrupt lines VIO-VI7. Attach the jumper wire from the pad connected to pin 4 of U44 to the desired DMA request line (schematic sheet 10). A jumper to VI6 is standard.

2-17

۹ ټ

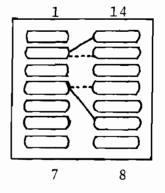

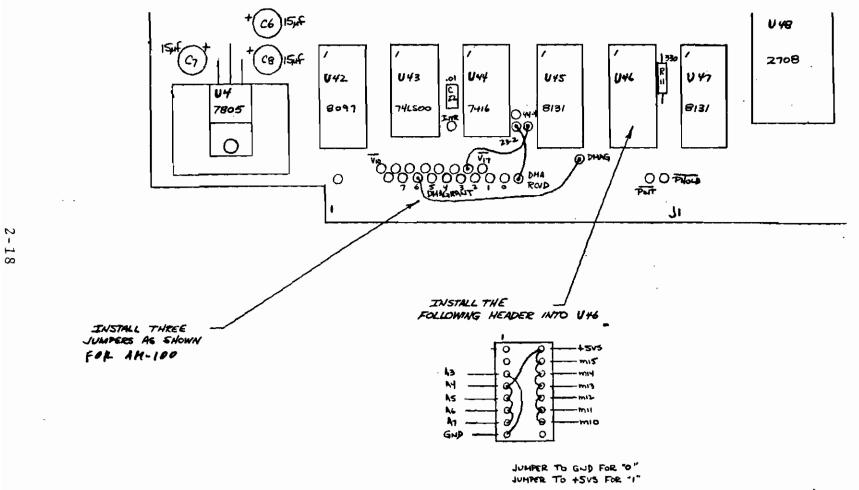

A3-A7 DETERMINE CONTECLLER I/O ADDRESS (FO STANDARD) MIO-MIS DETERMINE ROM STARTING ADDRESS (FLOO STANDARD)

Figure 2-4. Jumpers For Use With AM-100 System

<u>)</u>

#### 2.3.4 DMA RECEIVED.

DMA Received (DMARCVD) signal from the S-100 Bus must be jumper selected for proper CPU response to the AM-200 circuit board. Install the three jumpers as shown in Figure 2-4 and schematic sheets 8 and 10.

#### 2.3.5 DMA GRANT LINES.

DMA Grant response from the S-100 bus must be jumper selected to provide CPU response to the AM-200 circuit board. Attach the jumper from the pad connected to pin 6 of U25 to the desired DMA Grant line (schematic sheet 8) which is normally DMAGRANT 6.

#### 2.3.6 PHANTOM FEATURE.

A phantom feature can be used with the AM-200 Floppy Disk Controller. This feature is supported in operating system software release 3.0 and later and will not work if a Video Display Module (VDM) is being used for the software program Dystat because the system memory overlaps the VDM memory (see Alpha Micro Operating System AMOS Manual). Also, the memory board must support the phantom feature.

#### 2.3.6.1 APPLICATION.

Modification procedure to the AM-200 circuit board for the phantom feature cover two different configurations. Check the configuration level at your circuit board by the revision designation located on the component side of the board in the lower left quadrant just under the AM-200.

#### NOTE

For AM-200 circuit boards of Rev. B02 and later, use modification procedures in paragraph 2.3.6.2. For circuit boards earlier than Rev. B02, use modification procedures in paragraph 2.3.6.3. 2.3.6.2 MODIFICATION PROCEDURE FOR BOARDS OF REV. B02 AND LATER.

To provide the phantom feature for boards of Rev. BO2 and later, jumper pins 1 and 2 of the address header U46. To remove the phantom feature, remove the jumper.

2.3.6.3 MODIFICATION PROCEDURE FOR BOARDS EARLIER THAN REV. B02. Use the following procedure to modify AM-200 circuit boards earlier than rev. B02 to add the phantom feature. 5

#### NOTE

The primary 48K-64K memory in the system must have phantom option. If in doubt, contact the manufacturer.

- 1. Cut etch U35-8 to U40-10 at feedthru near U40-10 on back.

- 2. Jumper. a. U22-10 to J1-67 b. U22-11 to U23-13 c. U35-8 to U23-12 d. U40-10 to U23-11

- 3. Enable phantom on 48K-64K board in the primary bank only, remove jumper from all other.

- 4. If you do not have a PERLOD REV. D bootstrap PROM in your floppy controller, order specific PROMS from Alpha Micro.

- 5. PHANTOM will not work with VER. 2.0 and earlier software or AMSLOD REV. B or PERLOD REV. B. and earlier IPL (Indentured Parts List) PROMs.

6. The latest revision of the AM-100 IPL PROM currently in use is PERLOD REV. D which is released on diskettes starting with release 3.1\* This IPL PROM now loads either AMS or IBM format, automatically deciding which format the diskette is in.

\* Software supplied with Alpha Micro AM-100 systems.

#### 2.3.7 8080 AND CPM SYSTEM MODIFICATION.

When the AM-200 Floppy Disk Controller is used with 8080 systems, DMA jumpers must be as shown in Figure 2-5 (instead of Figure 2-4 for AM-100 systems). In addition, the following modifications to the AM-200 are required.

#### 2.3.7.1 APPLICATION.

This procedure is applicable to AM-200 Floppy Disk Controller Revisions A and B. Note the differences in the procedure for Revision A as compared to the procedure for Revision B.

#### 2.3.7.2 MODIFICATION PROCEDURE.

Use the following procedure to modify AM-200 circuit boards when used with 8080 systems.

- First determine if you have a REV. A or B board. If the board is a REV. B, skip step 2 and proceed with step 3.

- 2. If you have a REV. A board, the following jumper changes are required. All wiring changes will be to the solder side of the board.

- a. Cut short trace between U39-4 and U39-5.

- b. Cut other trace going to U39-4.

- c. Cut etch between U53-7 and U53-5.

- d. Jumper free end of trace just cut, to U39-3. See Figure 2-4.

- e. Run a jumper wire from U39-4 to U29-10.

- 3. Remove jumper wires in lower right corner of board and rewire according to the drawing in Figure 2-5.

- 4. Remove AM-100 IPL PROM and install the 8080 IPL PROM.

- 5. No jumper changes are needed on DIP header at U46.

- 6. The normal 8080 IPL PROM runs at FC00h. So when operating CP/M, examine FC00h and run. CP/M should come up with a sign-on message.

- 7. A special 8080 IPL PROM is available to run at F000h. If this is used, changes must be made to the DIP header at U46.

- 8. The console I/O ports are set up for use with the 3P+S and are the same as the AM-100 system. Ports and status bits are as follows:

| Control port :  | 00h                |

|-----------------|--------------------|

| Data port :     | 01h                |

| RDA :           | 02h                |

| TBE :           | 01h                |

| status bits are | all positive true. |

- 9. To improve the reliability of 8080 systems using AM-200 and CP/M, install a 1000 ohm 1/4 watt resistor as follows:

- a. Locate U43 pins 9 and 14. Connect the 1000 ohm resistor between these two pins. U43 should be a 74LS00, near the lower left hand corner of the board.

- b. This modification will not affect normal operation with the AM-100.

A3-A7 DETERMINE CONTROLLER Z/O ADDREES (FO STANDARD) MID-MIS DETERMINE ROM STARTING ADDREES (ROO STANDARD)

Figure 2-5. Jumpers For Use With 8080 System

Figure 2-7. AM-200 8080 Modification Wire Additions "A" Level Only.

## SECTION 3 PROGRAMMING

#### 3.0 INTRODUCTION.

This section describes the programming requirements for the AM-200 circuit board. Circuit board addressing, bootstrap loader, external control register, and disk format modification are described for complete system compatibility.

#### 3.1 ADDRESSING.

The AM-200 and its associated disk drives are addressed through the S-100 bus address lines. The circuit board address is jumper selectable by the plug-in header U46 from address lines A3-A7. Address lines A0 and A1 select the desired register in the disk controller module and A2 must be a zero to generate floppy controller enable (CE) signal.

Registers internal to the floppy disk controller module must be loaded with the proper control data for disk operation. These registers are loaded from the data access lines for read and write operations under control of address lines A0 and A1. See paragraph 4.2.1.1 for a complete description of these registers. Table 3-1 defines the I/O ports contained in the Floppy Controller.

#### 3.2 EXTERNAL CONTROL REGISTER.

The external control register must be loaded with control data to select the desired operation. To load the control register, address the card with bits A3-A7 and set A0=0, A1=1 and A2=1. The control register accepts control information from the CPU as shown in Table 3-2.

| I/O Port<br>Address* |                               | Output                           | Comments              |

|----------------------|-------------------------------|----------------------------------|-----------------------|

| FO                   | Status Register               | Command Register                 | See Paragraph 4.2.1.2 |

| F1                   | Track Register                | Track Register                   | See Paragraph 4.2.1.2 |

| F2                   | Sector Register               | Sector Register                  | See Paragraph 4.2.1.2 |

| F 3                  | Data Register                 | Data Register                    | See Paragraph 4.2.1.2 |

| F 4                  |                               | Registers Low<br>Byte**          |                       |

| F 5                  |                               | Registers High<br>Byte <b>**</b> |                       |

| F6                   | External Sta-<br>tus Register | External Control<br>Register     | See Table 3-2         |

Table 3-1. I/O Port Definitions

\*The base I/O Port address (shown as FO) is jumper selectable to any block of eight I/O addresses.

\*\*Either DMA Address Register or Byte Count Register. See External Control Register, bit 7.

## Bit Function 0 Select Drive 0 Select Drive 1 1 2 Select Drive 2 Select Drive 3 3 4 Sets stepping rate instead of disk controller (PerSci only) 5 Enables interrupts (used as phantom). Controls disk read or write: 6 1 = WRITE TO FLOPPY, 0 = READ FROM FLOPPY7 Selects DMA address register (Bit 7=0) or Subsector Register (Bit 7=1).

Table 3-2. External Control Register Data

See Table 3-3 and paragraph 4.2.1.2 for programming registers internal to the disk controller module (U12).

### Table 3-3. External Status Register Data

| Bit | Input Function               |  |  |  |

|-----|------------------------------|--|--|--|

| 4   | Subsector count register ≠ 0 |  |  |  |

| 7   | Seek complete                |  |  |  |

### 3.3 BOOTSTRAP LOADER.

The 8K PROM on the AM-200 circuit board contains the bootstrap loader program for system initialization. The base address for boot load is jumper selected by address header U46 (FCOO for PerSci and Wangco). To load the program, set this address on lines A10-A15 and sequence through the address block with address bits A0-A9.

### SECTION 4 FUNCTIONAL THEORY OF OPERATION

### 4.0 INTRODUCTION.

The AM-200 floppy disk controller board contains integrated circuit elements for the necessary data processing for the performance of functions as described in Sections 1, 2 and 3 of this manual. This section describes the functional theory of operation of the circuit board and also provides information for each of the integrated circuit elements.

### 4.1 CIRCUIT BOARD OPERATION.

This circuit board provides floppy disk control and interface capability that interfaces with the system S-100 bus to the CPU. An 8K PROM contains a bootstrap program for system startup.

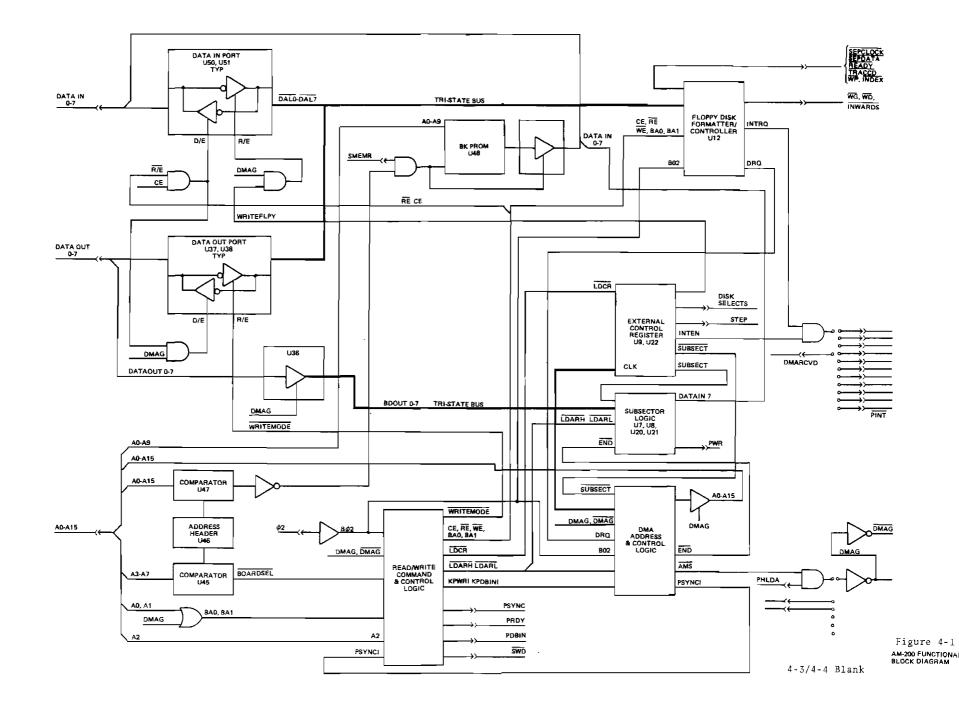

The functional block diagram is shown in Figure 4-1 and the circuit board schematic is contained in Section 6 of this manual. Table 4-1 contains a list of the signals used in this circuit board with definitions of their functions.

For S-100 Bus Interface Signals see Table 2-2. For Floppy Disk Interface Signals see Table 2-3. For Floppy Formatter/Controller Signal descriptions see Table 4-2.

# Table 4-1. AM-200 Circuit Board Signal List

| SIGNAL               | NAME                             | SCHEM PAGE<br>OF SOURCE | FUNCTION                                                                                                                     |

|----------------------|----------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| AO-A15               | Address Bit 0-<br>Address Bit 15 |                         | S-100 Bus Address Lines.                                                                                                     |

| AMS                  | Activate<br>Memories             | 10                      | Generates jumper selected<br>DMA request to bus master.                                                                      |

| BAO, BA1             | Buffered<br>Address 0 & 1        | 6                       | Sets decoder to generate<br>address load commands.                                                                           |

| BDOUT 0 -<br>BDOUT 7 | Buffered Data<br>Out Bits 0-7    | 2                       | Buffered CPU output data.                                                                                                    |

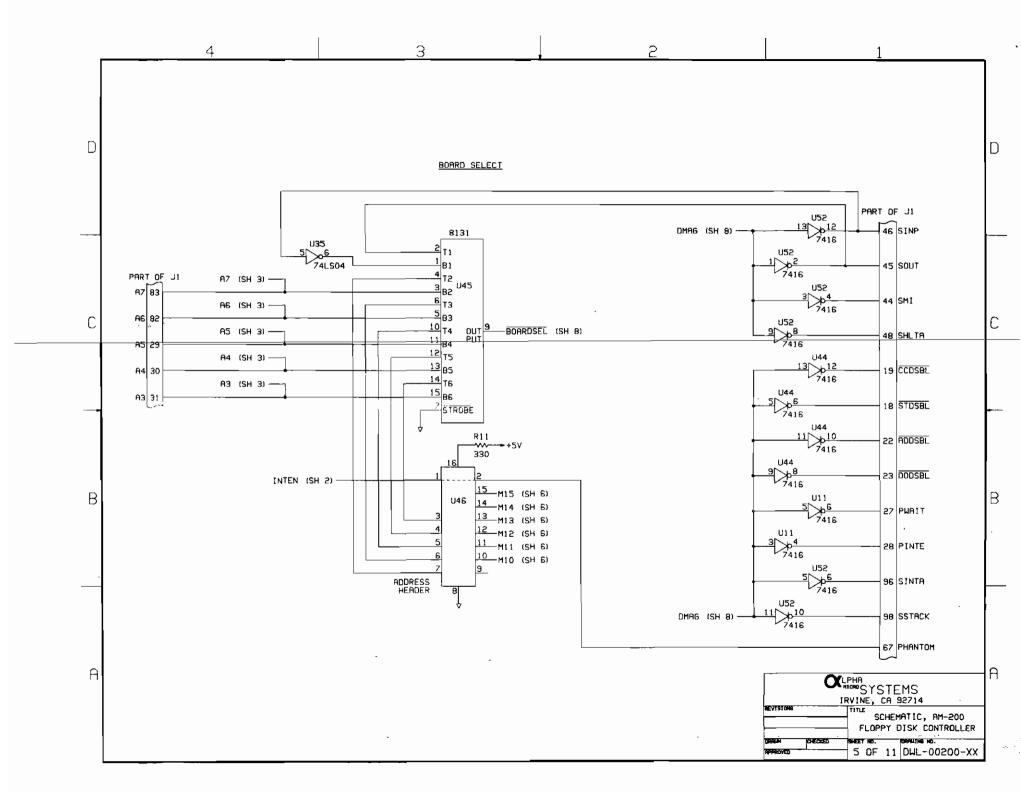

| BOARDSEL             | Board Select                     | 5                       | Output of board address com-<br>parator. Asserted when S-100<br>I/O Address matches I/O<br>address wired in header.          |

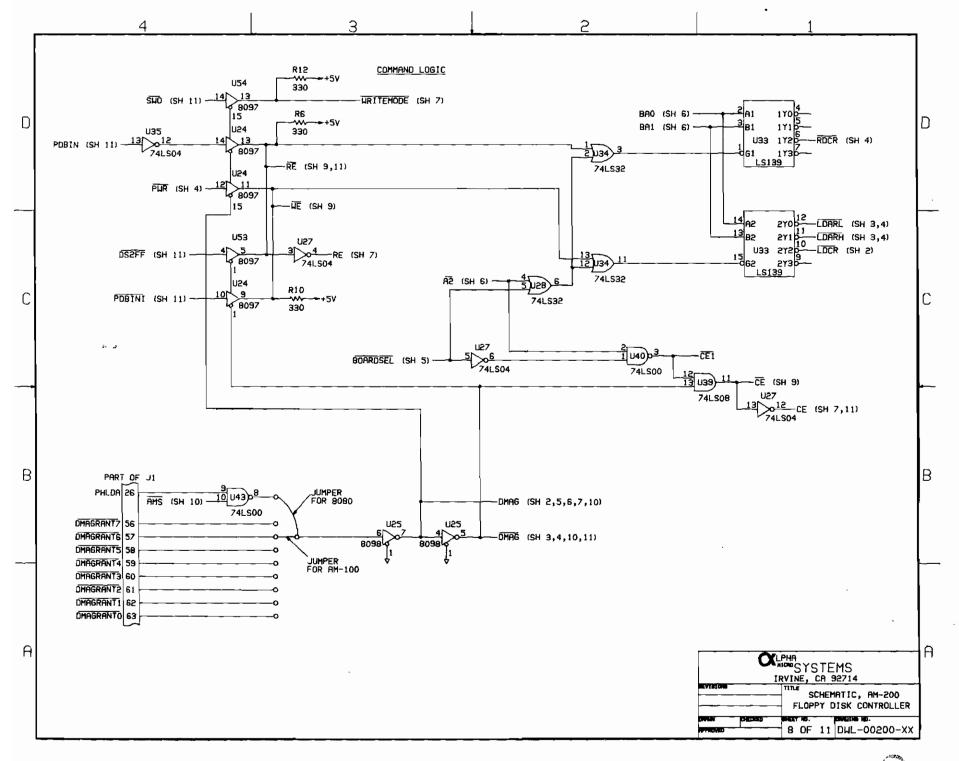

| CE, CE               | Chip Enable                      | 8                       | Enables Floppy Disk Formatter/<br>Controller, Data Ports, and<br>conditionally sets PRDY.                                    |

| CE1                  | Chip Enable 1                    | 8                       | True when the board has been addressed ( $\overline{BOARDSEL}$ ) and $\overline{A2}$ is high. Used to make $\overline{CE}$ . |

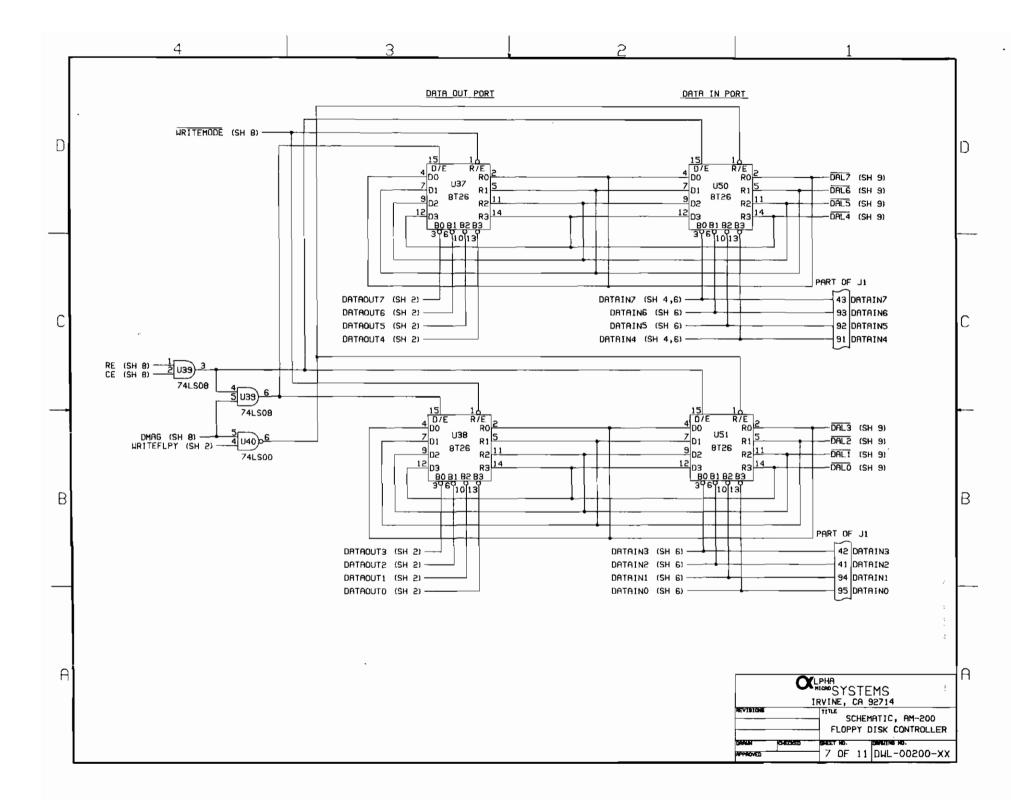

| DALO-DAL7            | Data Access<br>Lines             | 7,9                     | Eight bit bi-directional bus<br>used for transfer of data,<br>control and status information.                                |

## Table 4-1 (Cont.). AM-200 Circuit Board Signal List

٢

| SIGNAL                 | NAME                          | SCHEM PAGE<br>OF SOURCE | FUNCTION                                                                                                                                     |

|------------------------|-------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| DATAINO-<br>DATAIN7    | Input Data<br>Bits 0-7        | 4, 6, 7                 | Bus Master input data Port.                                                                                                                  |

| DATAOUT0 -<br>DATAOUT7 | Output Data<br>Bits 0-7       | 2                       | Bus Master output data Port.                                                                                                                 |

| DMAG,<br>DMAG          | DMA Grant                     | 8                       | Jumper selectable from S-100<br>DMAGRANT lines. Sets DMA<br>priority level for AM-200.<br>Level must match VIx level<br>used to request DMA. |

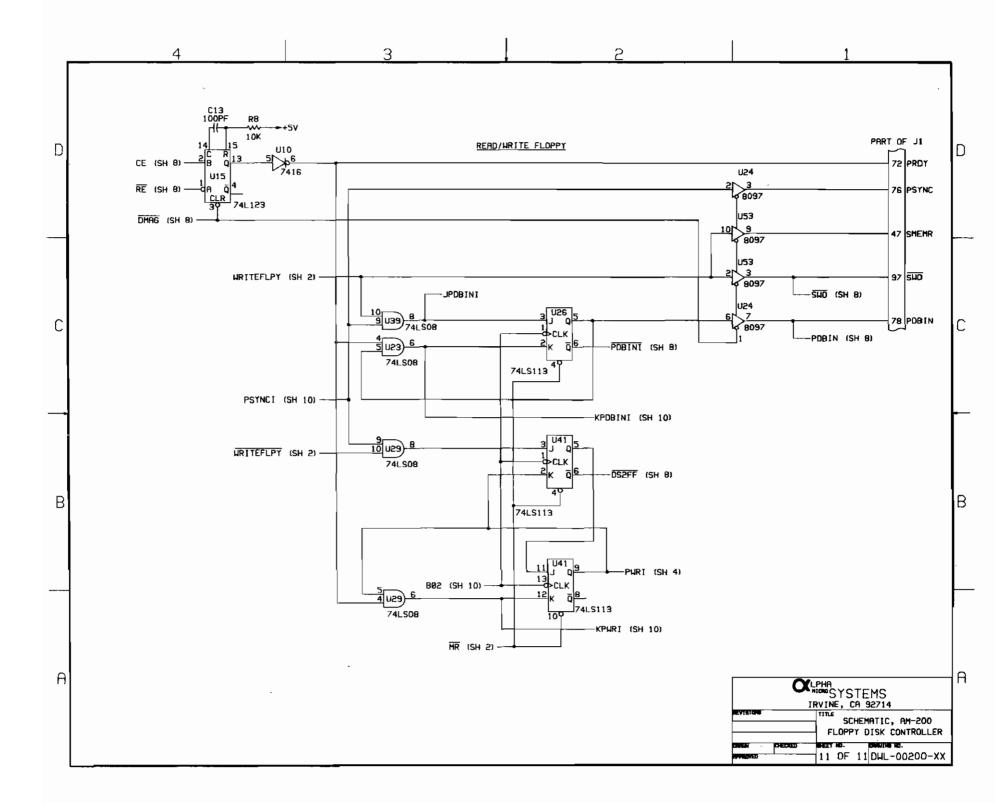

| DS2FF                  | Read From<br>Floppy           | 11                      | Generates Read Enable signal<br>and sets PWRI flip-flop.                                                                                     |

| END                    | End                           | 10                      | Controls DMA address register<br>and subsector register.<br>Stops sequencing when high.                                                      |

| INTEN,<br>INTEN        | Interrupt<br>Enable           | 2                       | External control register bit<br>5 output to enable S-100<br>interrupts.                                                                     |

| JPDBINI                | Data Bus Inset                | 11                      | Sets Data Bus in flip-flop(J).                                                                                                               |

| KPDBINI                | Data Bus Inset                | 11                      | Resets Data Bus In flip-flop<br>(K).                                                                                                         |

| KPWRI                  | PWRI Reset                    | 11                      | Resets PWRI flip-flop (K)                                                                                                                    |

| LDARH                  | Load Address<br>Register High | 8                       | Loads higher 8 bits of sub-<br>sector address register and<br>DMA address register.                                                          |

Table 4-1 (Cont.). AM-200 Circuit Board Signal List

|         |                              | SCHEM PAGE |                                                                                      |

|---------|------------------------------|------------|--------------------------------------------------------------------------------------|

| SIGNAL  | NAME                         | OF SOURCE  | FUNCTION                                                                             |

| LDARL   | Load Address<br>Register Low | 8          | Loads lower 8 bits of sub-<br>sector address register and<br>DMA address register.   |

| LDCR    | Load Control<br>Register     | 8          | Provides clock input to load<br>external control register<br>from DATAOUT 0-7 lines. |

| MR, MR  | Master Reset                 | 2.         | Resets circuit card.                                                                 |

| M10-M15 | Address lines                | 5          | Jumper selected output from<br>address header to comparator<br>for PROM selection.   |

| PDBIN   | Data Bus In                  | 11         | Read strobe.                                                                         |

| PDBINI  | Data Bus In<br>Inverted      | 11         | Inverted read strobe.                                                                |

| PSYNCI  | PSYNC Internal               | 10         | Generates PSYNC output through<br>gate (DMAG) and begins bus<br>cycle.               |

| PWR     | Write Strobe                 | 4          | 0 = Bus Master is writing.                                                           |

| PWRI    | PWR Internal                 | 11         | Generates write strobe (PWR)<br>when subsector is non-zero.                          |

| RDCR    | Read Control<br>Register     | 8          | Gates DATAIN 4 and 7 when<br>External Control register<br>is to be read by CPU.      |

Table 4-1 (Cont.). AM-200 Circuit Board Signal List

4

٠£

| SIGNAL                 | NAME                             | SCHEM PAGE<br>OF SOURCE | FUNCTION                                                                                                                                  |

|------------------------|----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RE, RE                 | Read Enable                      | 8                       | Initiates a read mode in the<br>Disk Controller DIP, enables<br>the Data In Port with an<br>active CS, and sets PRDY to<br>the S-100 bus. |

| STEP,<br>STEP          | Disk Head Step                   | 2                       | Controller output pulses for<br>stepping of disk read/write<br>head.                                                                      |

| SUBSECT<br>SUBSECT     | Selects<br>Subsector<br>Register | 2                       | Selects either of two 16 bit<br>registers for addressing by<br>the CPU. O=DMA Address Regis-<br>ter, 1=Subsector Count Regis-<br>ter.     |

| SWO                    | Write Output<br>Status           | 11                      | Output indicating Bus Master<br>is in Write Mode.                                                                                         |

| WE                     | Write Enable                     | 8                       | Sets the Data Access Lines to<br>the write mode with an active<br>CS to the Disk controller DIP.                                          |

| WRITEFLPY<br>WRITEFLPY |                                  | 2                       | Mode control for DMA logic to<br>either read from or write to<br>floppy disk.                                                             |

| WRITE<br>MODE          | Write Mode                       | 8<br>*                  | Sets Receiver Enables in Data<br>Out Port when in Write Mode.<br>Generated from SWO at DMAG.                                              |

#### 4.1.1 ADDRESSING.

Address data is received from the S-100 bus on lines AO-A15. The address lines provide one input to comparators U45 and U47. The other inputs come from address header U46, which generates address codes from jumpers on an address block permitting user selection of the circuit board I/O address. The address coding jumper wires are connected to either +5V or ground to generate the selected address. Signal BOARDSEL is asserted when the input address from the address lines compare with the address of the card. This generates Chip Enable (CE) signals in the command and control logic.

The board I/O address is contained on address lines AO-A7 (normally FO). The first four addresses (AO-A1) are contained on the disk controller module U12. Address line A2 must be a 0 to enable CE generation and lines A3-A7 generate BOARDSEL through comparator U45 and header U46.

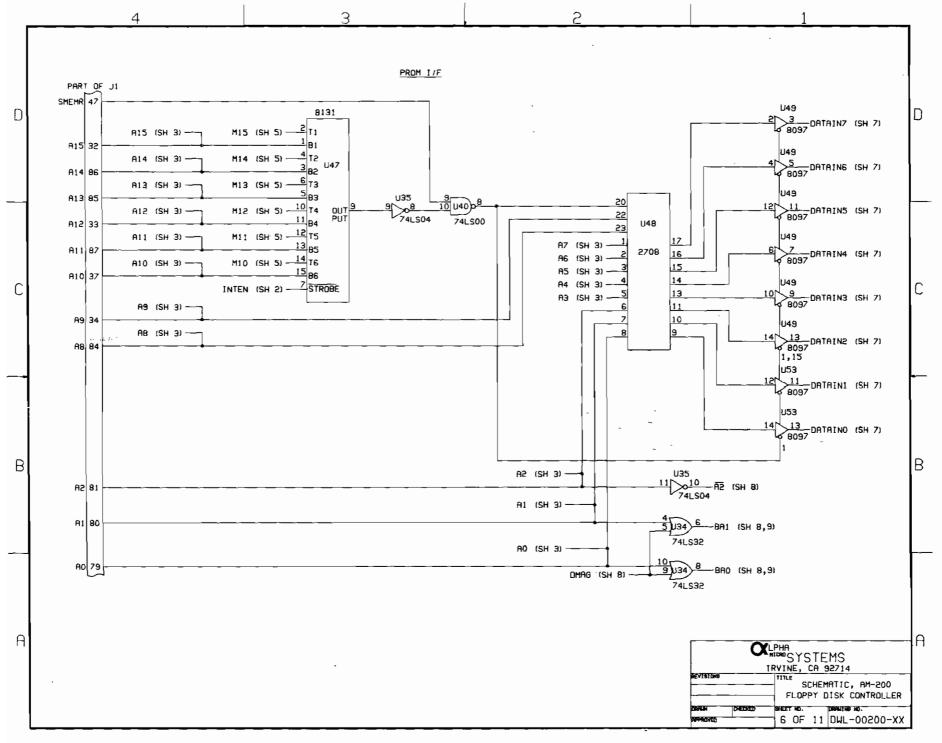

Addressing for the 8K PROM (U48) is handled by comparator U47 and Header U46. The base address of the PROM is jumper selectable and is normally configured for address FC00 for Per-Sci drives.

4.1.2 BOOTSTRAP PROM.

The 8K PROM (U48) contains the bootstrap program for floppy disk operation. The base address is selected by U46 which enables PROM operation with receipt of Memory Read Status (SMEMR) signal from the S-100 bus. Address lines A0-A9 then sequence through the memory and load the contents of the PROM into the system CPU, through gated drivers, U49 and U53 to DATAIN 0-7 lines.

4.1.3 EXTERNAL CONTROL REGISTER.

The external control register (U9 and U22) must be loaded with data for the AM-200 to execute the desired functions. The external control register consists of eight D flip-flops connected to data lines BDOUTO-BDOUT7. The clock input is Load Control Register (LDCR) signal generated from Buffered Address Bits BA0 and BA1 through decoder U33 (BA0=0, BA1=1). The decoders are enabled by  $\overline{PWR}$ ,  $\overline{A2}$  and  $\overline{BOARDSEL}$ .

4 Ê

The functions loaded into the register with their corresponding bit locations are as follows:

| Bit | Mnemonic  | Function                                  |

|-----|-----------|-------------------------------------------|

| 0   | DS1L      | Select Drive O                            |

| 1   | DS1R      | Select Drive 1                            |

| 2   | DS2L      | Select Drive 2                            |

| 3   | DS2R      | Select Drive 3                            |

| 4   | STEP      | Controls stepping rate instead of Disk    |

|     |           | Controller (PerSci only)                  |

| 5   | INTEN     | Enables Interrupts                        |

| 6   | WRITEFLPY | Controls Disk read or write               |

| 7   | SUBSECT   | Selects DMA address Register (Bit 7=0) or |

|     |           | subsector count register (Bit 7=1).       |

For a control register loading operation to take place, the circuit card must be addressed with address lines A2=1, A1=1, A0=0, and BOARDSEL. The PWR signal through U34 generates  $\overline{\text{LDCR}}$  which loads the register.

4.1.4 SUBSECTOR REGISTER LOGIC. Subsector logic consists of a 16-bit up/down counter with control logic. The counter is wired to count down only from its preset state.

This register is loaded before each read command to the floppy drive with one less than the number of bytes to be read from the desired sector. Loading is accomplished by setting bit 7 of the control register to a 1. Combinations of Address lines A0 and A1 generate load commands  $\overline{\text{LDARL}}$  and  $\overline{\text{LDARH}}$  from the command logic decoder. The settings are A0=0, A1=0 for the lower byte  $\overline{\text{LDARL}}$  and A0=1, A1=0 for the upper byte LDARH.

The subsector register is decremented after each byte is transferred from the disk into memory or vice versa. When the register underflows, no more write pulses are transferred. The Borrow output of U21 then sets Bit 7 (DATAIN7) indicating the end of the subsector.

### 4.1.5 DMA ADDRESS AND CONTROL.

This 16-bit register consists of up/down counters U5, U6, U18, and U19 that are wired to always count up from its preset state. Loading and operation is similar to the subsector register except that the DMA address register operates on the opposite state of control register bit 7 (bit 7=0).

The DMA register is loaded with the initial memory address from BDOUT lines for data transfer to or from the floppy disk. The register is incremented by the  $\overline{\text{END}}$  signal after each byte of data is transferred. The register output is wired to the 16 address lines AO-A15.

### 4.1.6 FLOPPY DISK FORMATTER/CONTROLLER.

The floppy disk formatter/controller module consists of a Western Digital FD1771 module that interfaces the AM-200 with the floppy disk drive. Control and data logic support module operation and provide complete S-100 bus system interface.

The module data lines are connected to tri-state bus lines DAL0-DAL7 for data transfer of both read and write cycles.

Chip select (CE), read or write enable, clock etc. are supplied by the AM-200 logic. Separate data and clock and floppy disk control signals interface directly with the module.

For a complete description of the module and its operation, see paragraph 4.2.1.

4.1.7 DISK READ AND WRITE SEQUENCE.

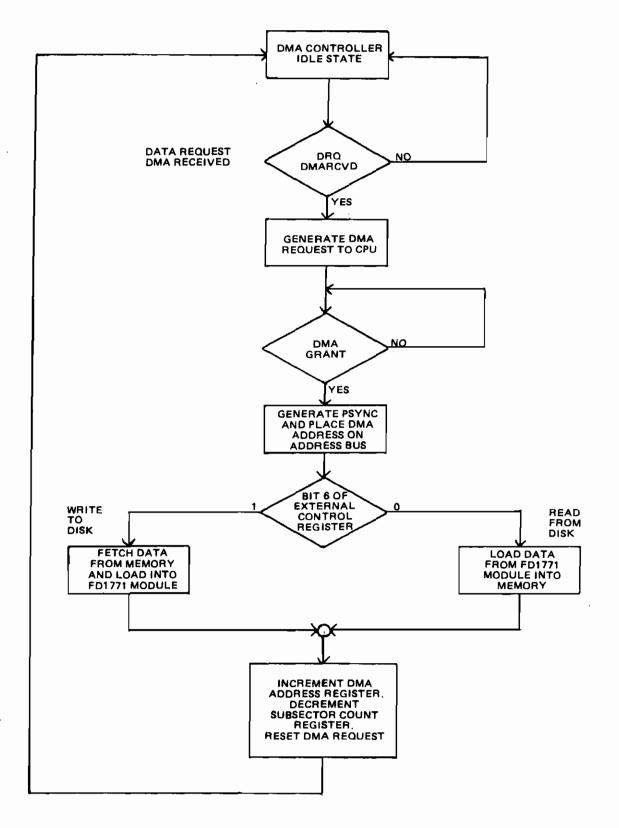

DMA transfer is initiated by a Data Request signal (DRQ) from the floppy Disk Controller module indicating that it is ready for more data from memory or has received more data from the disk. If DMARCVD is high, DRQ sets the AMS flip-flop and generates an interrupt on the selected line indicating a DMA request. The DMARCVD signal notifies all other DMA controllers on the bus that a DMA exchange is in process so they will not issue a DMA request. The AM-200 then waits until a DMA Grant (DMAG) signal is received from the CPU.

When the DMAG signal is received, it sets flip-flop U16 pin 5 which sets DMA flip-flop U16 pin 8. This generates a pulse that sets PSYNCI flip-flop and generates the PSYNC output to the CPU. At the same time, the DMA register output is placed on address lines AO-A15 indicating the current memory address of data transfer. A data transfer cycle begins for either disk read or write depending on the state of bit 6 of the control register. When a byte of data is transferred, END signal increments the DMA address register, decrements the subsector register and resets the DMA and AMS flip-flops. The AM-200 then waits for another DRQ and <u>DMAGRANTx</u> to repeat the cycle.

When the subsector register decrements past zero, it underflows and sets DATAIN7 indicating the end of a subsector block of data. This sequence is illustrated in Figure 4-2.

2

Figure 4-2. Disk Read and Write Sequence Flow Diagram

### 4.2 CIRCUIT MODULE DESCRIPTION.

This section describes the operation of the individual circuit packages (DIPS) contained on the AM-200 circuit board. Most of the data processing is handled by the Floppy Disk Formatter/ Controller module so it is described in detail. The control logic and interface modules are also described with logic and connection diagrams for each one.

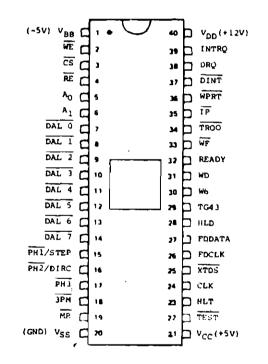

4.2.1 FLOPPY DISK FORMATTER/CONTROLLER DESCRIPTION (U12). This device performs the function of interfacing a processor to a flexible (Floppy) diskette drive. It provides the data accessing controls and the bidirectional transfer of information between the processor's memory and the magnetically stored data on the diskette. The diskette data is stored in a data entry format compatible with the IBM 3740 specification (other formats may be used providing more data storage). In this format all information is recorded on tracks (radial paths) in sectors (arc sections) defined by a programmed header. Module pin connections are shown in Figure 4-3 and signals are described in Table 4-2.

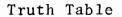

The device handles single density frequency modulated (FM) data. Each data cell is defined by clock pulses. A pulse recorded between clock pulses identifies the presence of a logic 1 bit; the absence of this pulse is interpreted as a logic 0 bit. The Address Marks for Index, ID, and Data are identified by a particular pattern not repeated in the remainder of the ID field or Data field. This is accomplished by reading patterns that are recorded with missing clock bits (logic 0) as shown below:

| Index Address Mark | Data  | 1 1 1 1 1 1 0 0                                               | =FC   |

|--------------------|-------|---------------------------------------------------------------|-------|

|                    | Clock | 1 1 0 1 0 1 1 1                                               | = D 7 |

| ID Address Mark    |       | $\begin{array}{c}1&1&1&1&1&1&0&1\\1&1&0&0&0&1&1&1\end{array}$ |       |

| Data Address Mark |       | $\begin{array}{c} 1 \ 1 \ 1 \ 1 \ 1 \ 0 \ 1 \ 1 \\ 1 \ 1 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \end{array}$ |       |

|-------------------|-------|-----------------------------------------------------------------------------------------------|-------|

| Deleted           |       | 1 1 1 1 1 0 0 0                                                                               |       |

| Data Address Mark | Clock | $1 \ 1 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1$                                                               | = C 7 |

These patterns are used as synchronization codes by the device when reading data and are recorded by the formatting command, Write Track, when the device is presented with data F7 through FE.

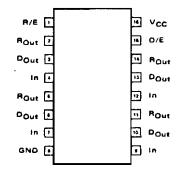

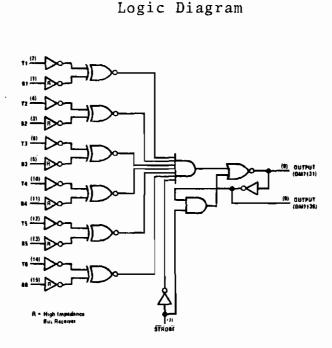

Figure 4-3. Floppy Disk Formatter/Controller Pin Connections

۰. :

# Table 4-2. Floppy Disk Formatter/Controller Signal List

I.

| SIGNAL                               | PIN  | FUNCTION                                                                                                                                       |

|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| VBB                                  | 1    | -5V power input                                                                                                                                |

| WE<br>WRITE ENABLE                   | 2    | Sets the DAL in the write mode<br>with an active CS (Chip Select)<br>signal.                                                                   |

| CS<br>CHIP SELECT                    | 3    | Active low selects the module and<br>enables CPU communication with the<br>device.                                                             |

| RE<br>READ ENABLE                    | 4    | Initiates the Read mode to search<br>for a track and sector code in the<br>ID field equal to that in the track<br>and sector registers.        |

| A <sub>0</sub><br>REGISTER ADDRESS 0 | 5    | Register address line 0 for access-<br>ing the active registers with $\overline{CS}$ ,<br>$\overline{RE}$ and $\overline{WE}$ . See Table 4-3. |

| A <sub>1</sub><br>REGISTER ADDRESS 1 | 6    | Register address line 1 for access-<br>ing the active registers with $\overline{CS}$ ,<br>$\overline{RE}$ and $\overline{WE}$ . See Table 4-3. |

| DALO-DAL7<br>DATA ACCESS LINES       | 7-14 | Data Access Lines Bits 0-7.                                                                                                                    |

| PH1/STEP<br>PHASE 1/STEP             | 15   | Phase 1 output for 3 phase stepping<br>motors or stepping rate for step-<br>direction motors.                                                  |

Table 4-2 (Cont.). Floppy Disk Formatter/Controller Signal List

| SIGNAL                              | PIN | FUNCTION                                                                                                                                             |

|-------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PH2/DIRC<br>PHASE 2/                | 16  | Phase 2 output for 3 phase stepping<br>motors or level to determine direc-<br>tion for step-direction motors.<br>O=step in 1=step out.               |